Based on the success of porting MiSTer already from DE10-Nano to DE10-Standard FPGA I had a tought why not port to DE1-SoC Altera Cyclone V FPGA as well?

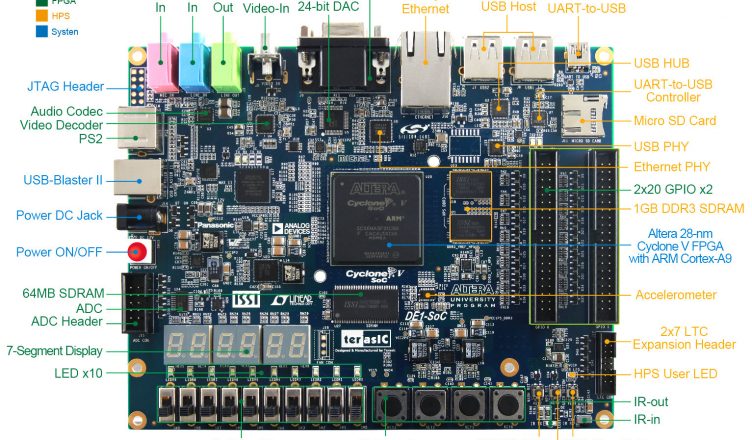

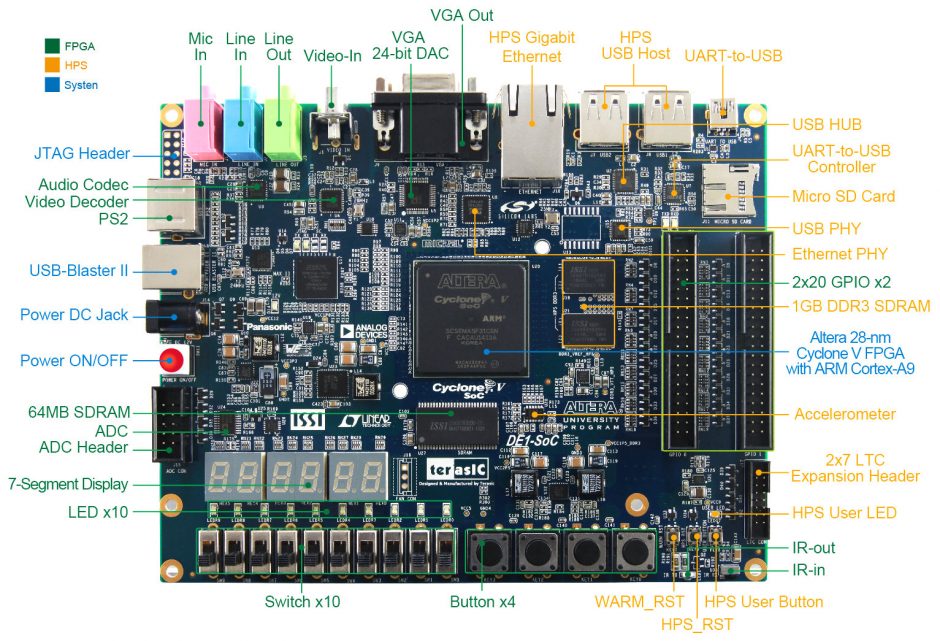

MiSTer is a cool project published originally by Sorgelig on Github and the FPGA code + project binaries only focused on DE10-Nano board, which is a great board: low price + HDMI output and ability to expand with SDRAM and Daughter board for VGA and Audio jack, but my idea was to put available this nice project on other FPGA boards as well, for example now on DE1-Soc. This boards feature point of view rich for an FPGA platform: 64MB SDRAM, VGA and audio output.

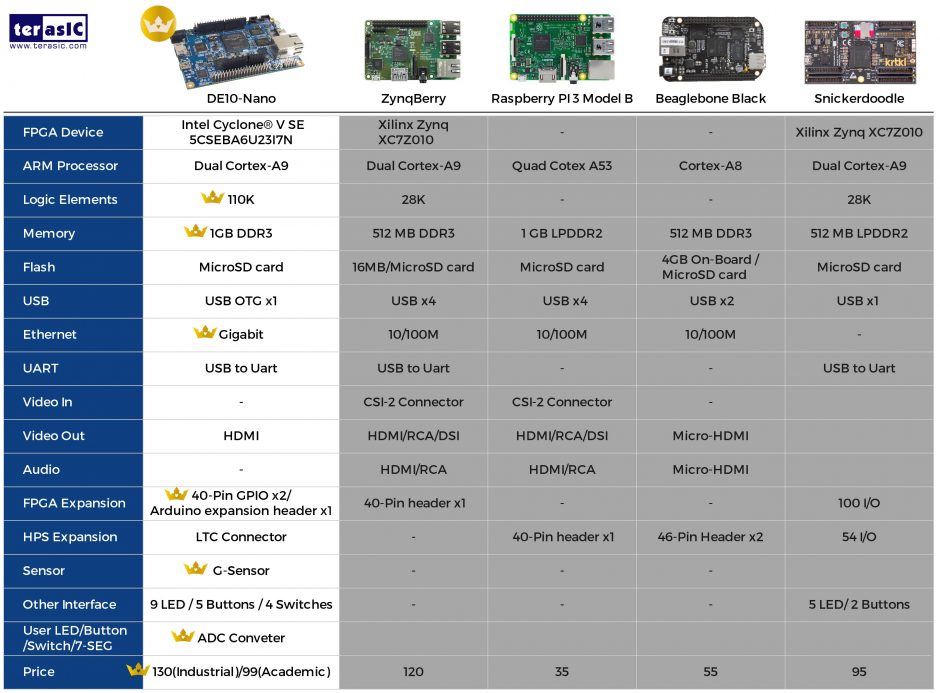

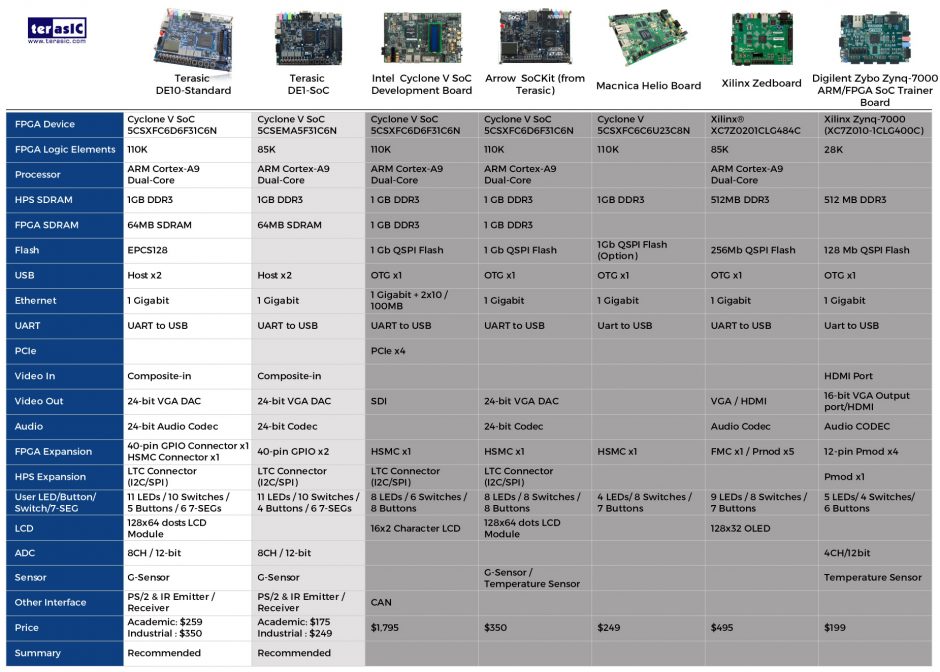

Quick re-cap about features of FPGA boards Nano vs Standard vs SoC

You can see from the feature list that DE1-SoC has the following additions comparing to DE10-Nano:

- built-in 64 MB SDRAM (this is important for retro cores emulation)

- built-in 24bit VGA output DAC for crystal clear VGA retro output

- built-in Wolfson 8731 audio DAC for crystal clear analogue output

- UART-USB onboard bridge from a FT232R chip – for easy serial console on USB port

- 2X standard size USB port that you can use to plug your USB Keyboard / Controller directly without necessary need of USB Hub

- Cyclone V SX SoC—5CSXFC6D6F31C6N: it has 110K LEs, 41509 ALMs – biggest on the consumer market this segment – similar like DE10-Nano.

There are two drabacks:

- not equipped with is HDMI. If you build multi function FPGA board for running retro computers – who cares?

- less logical elements exists on the board, while DE10-Nano and DE10-Standard had 115K, this board features only 85K, which is still above the average on the FPGA market. It just put the developers and porting a bit challenging and trickier 🙂

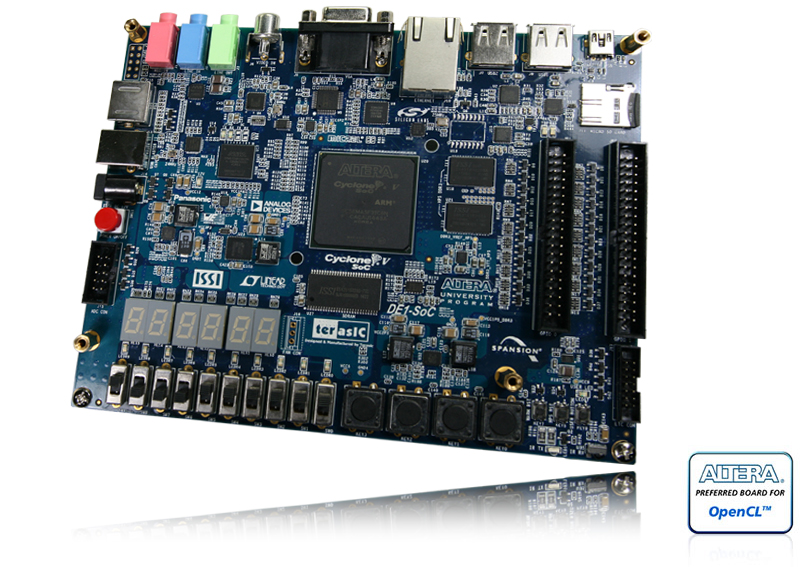

DE1-Standard is a beautiful and feature rich board to start with as well:

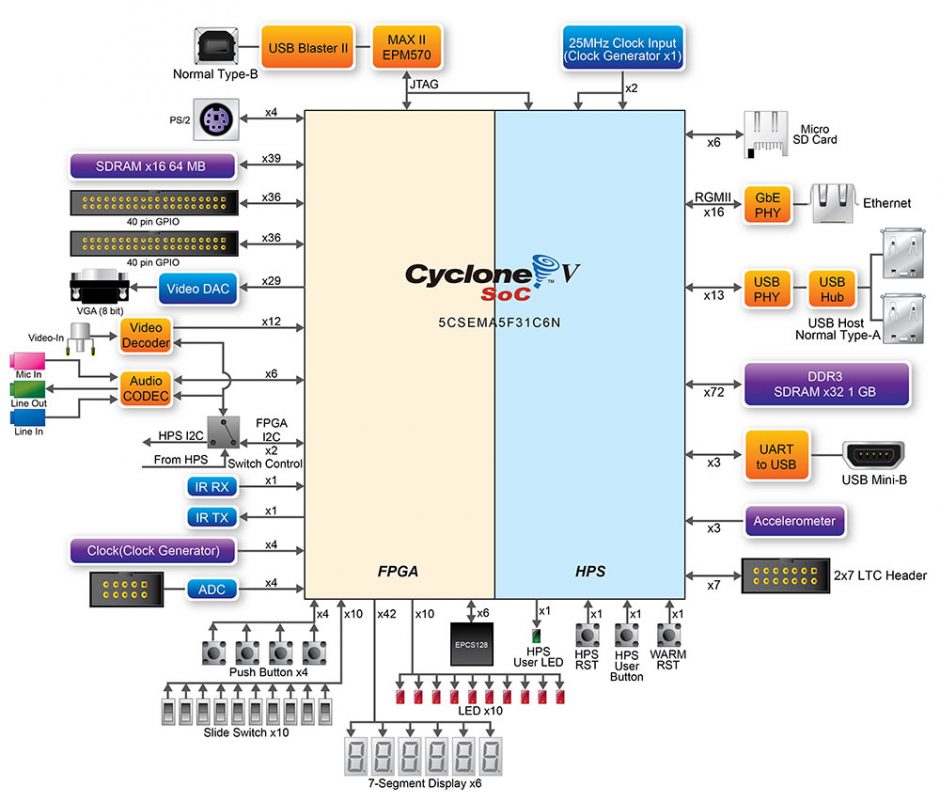

DE1-SoC architecture is similar like Nano, dual architecture: FPGA which running the binary and HPS (ARM which running the Linux)

Used Quartus software to port / develop further the ported DE10-Standard Core, which ported originally from MiSTer code.

DE1-SoC port of MiSTer released on Github

https://github.com/MiSTer-DE1-SoC/Main_MiSTer/wiki