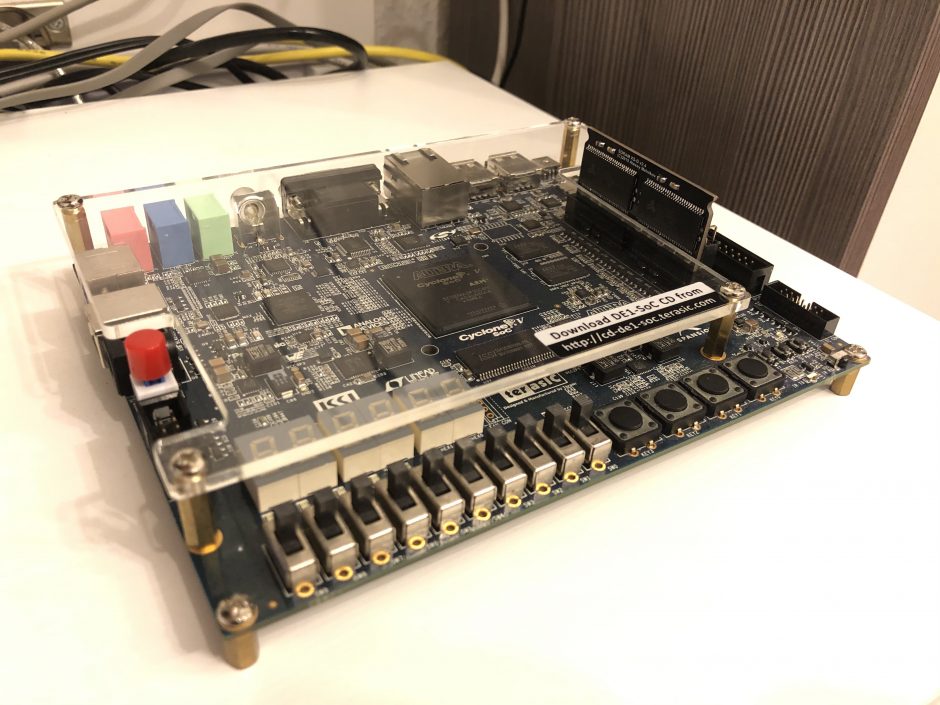

If you want to play for example with Metal Slug 3 under NeoGeo – you cannot skip this expansion board: The Vertical 128MB MiSTer SDRAM Board expansion board working well on Altera DE10-Standard, DE1-SoC and Arrow SoCKIT FPGA-s. If you want to leverage the 128MB expansion and want use in your custom FPGA board, you will need to rise the SDRAM module, because on DE10-Standard/DE1-Soc the GPIO 40 pin headers manufactured with plastic frame around, while that plastic frame not exists on DE10-Nano, so please follow the guide below howto install the riser.

Requirements:

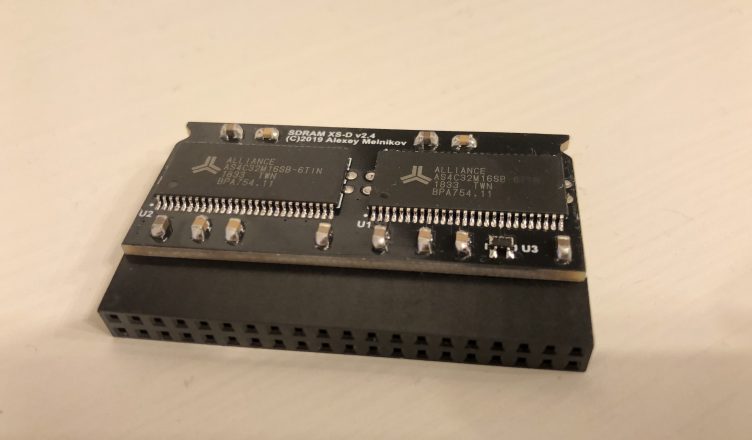

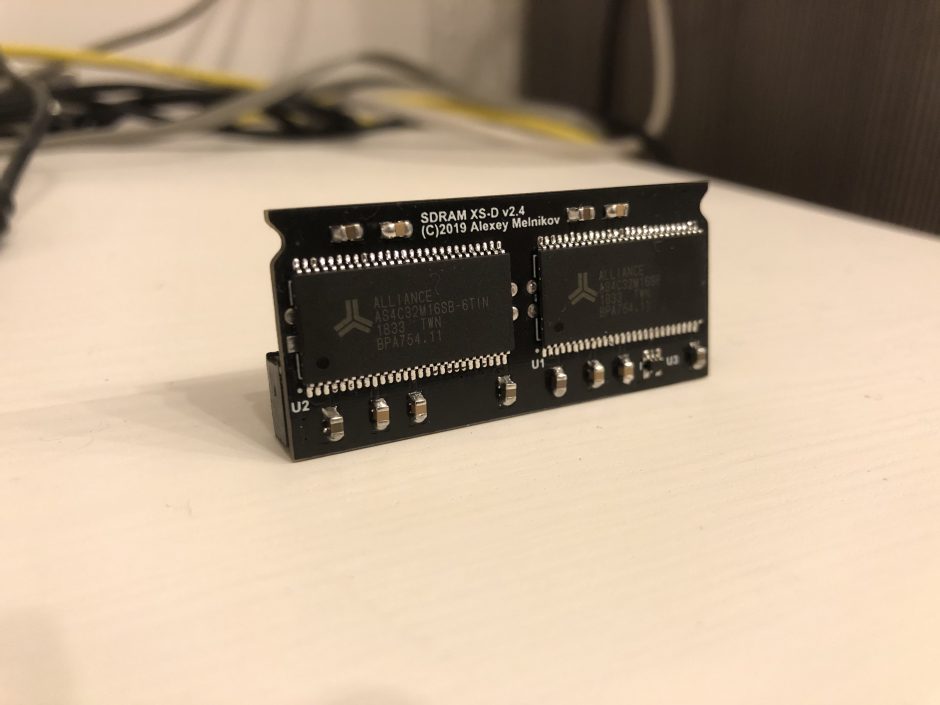

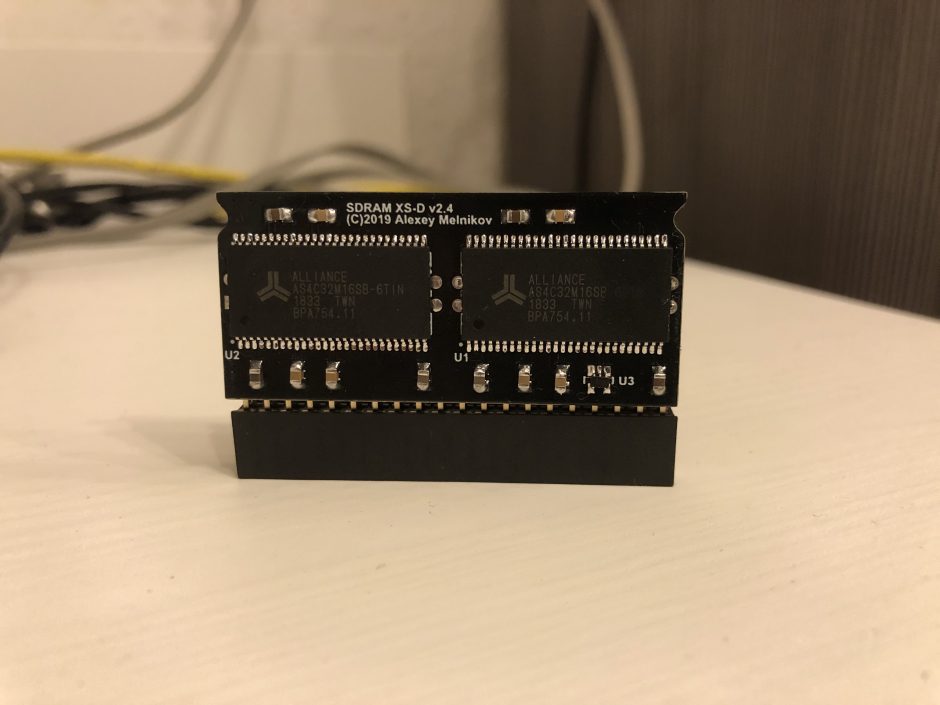

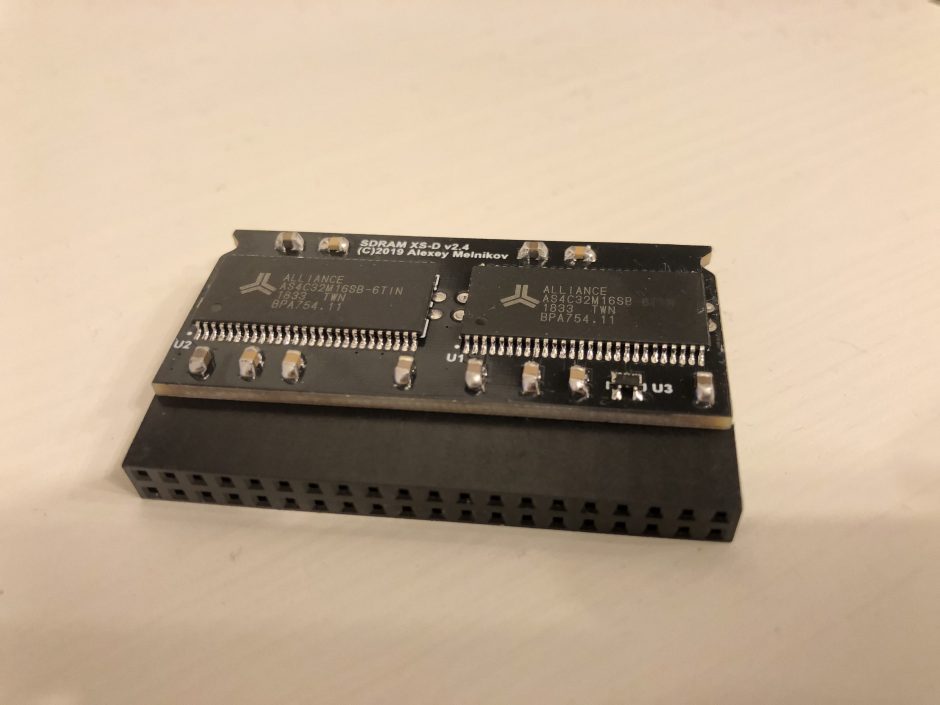

- SDRAM board: XS-D v2.4 / v2.5 or newer SDRAM board (128 or 64 Megabyte version)

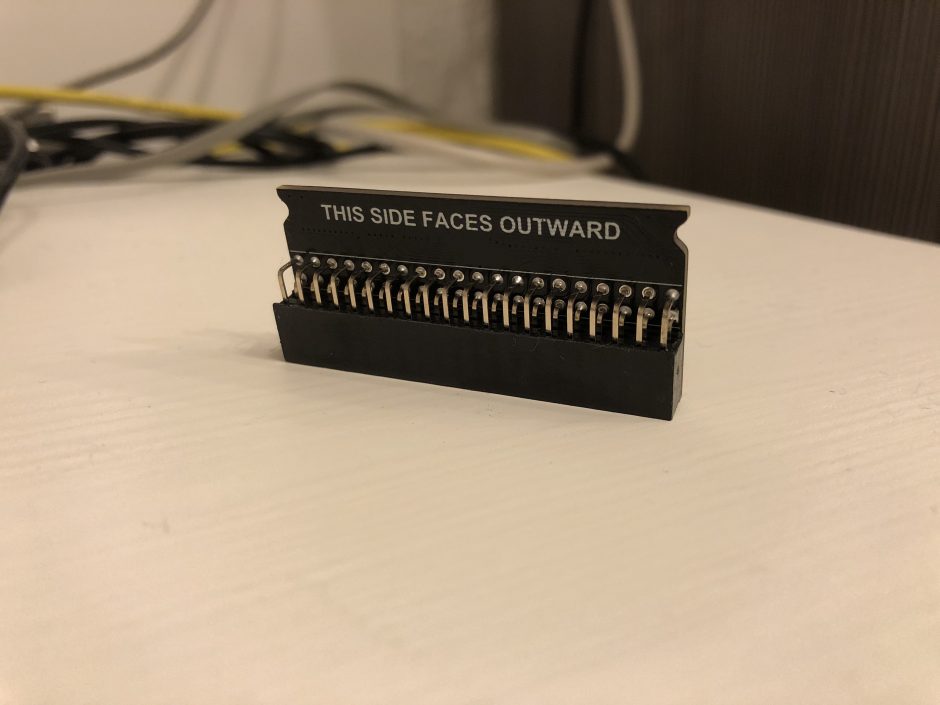

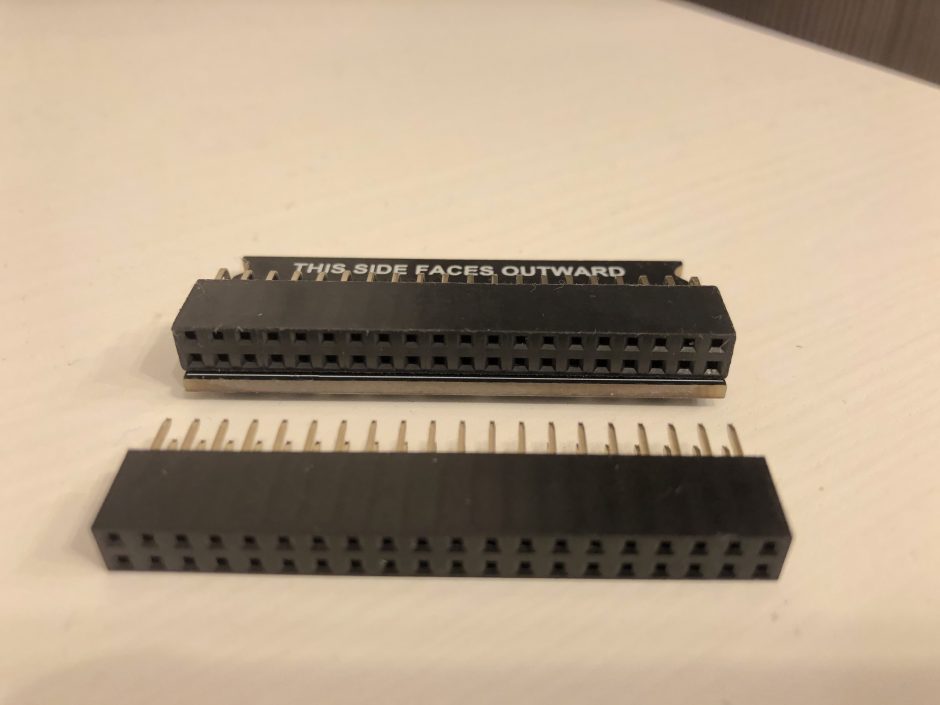

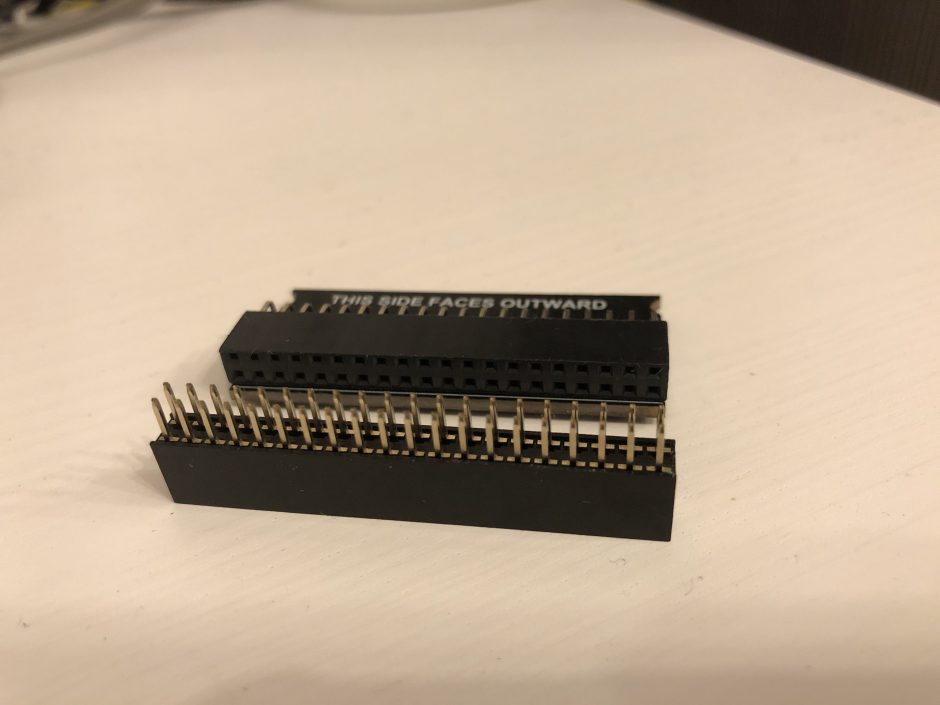

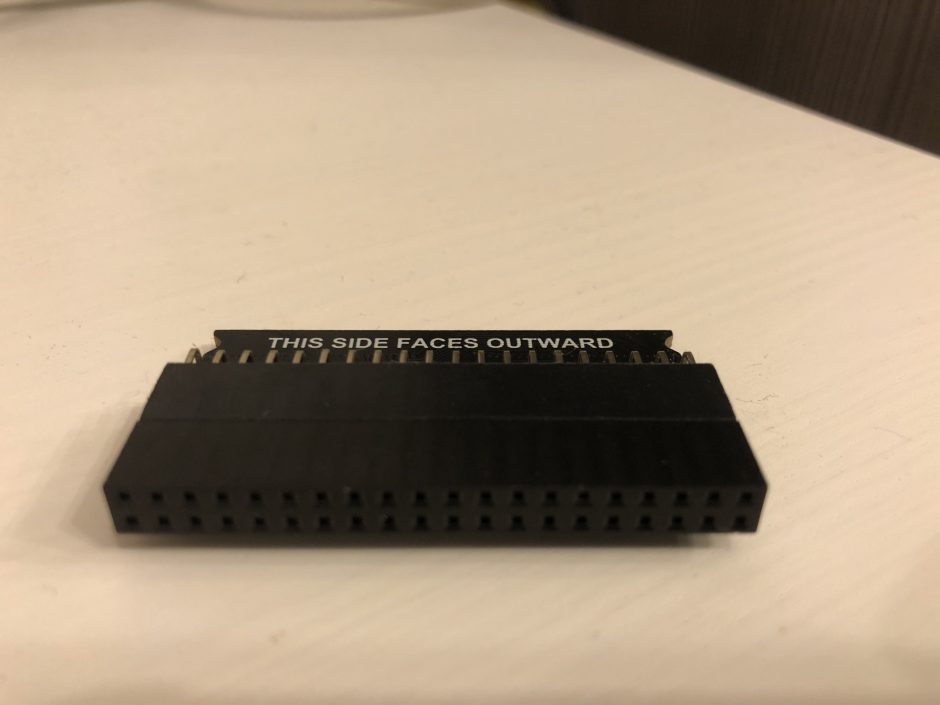

- GPIO Extender: 2×20 GPIO Socket Riser Header

- FPGA: Altera DE10 Standard or Altera DE1-SoC or Arrow SoCKit

- GPIO-HSTC/HSMC: In case of Arrow SoCKit: have to place GPIO-HSMC daughter board to FPGA’s HSMC port

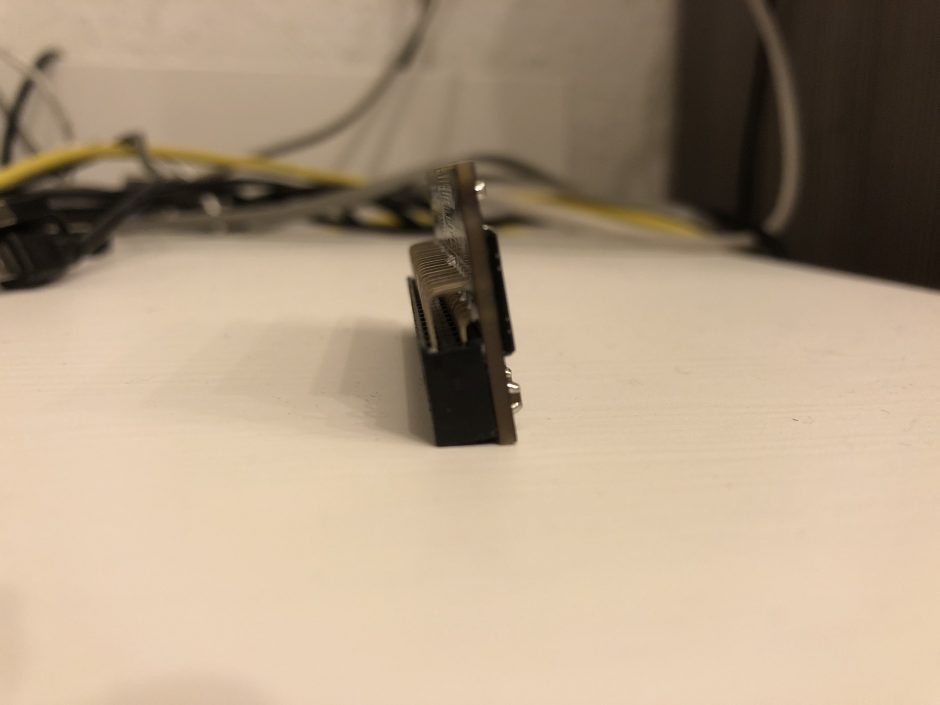

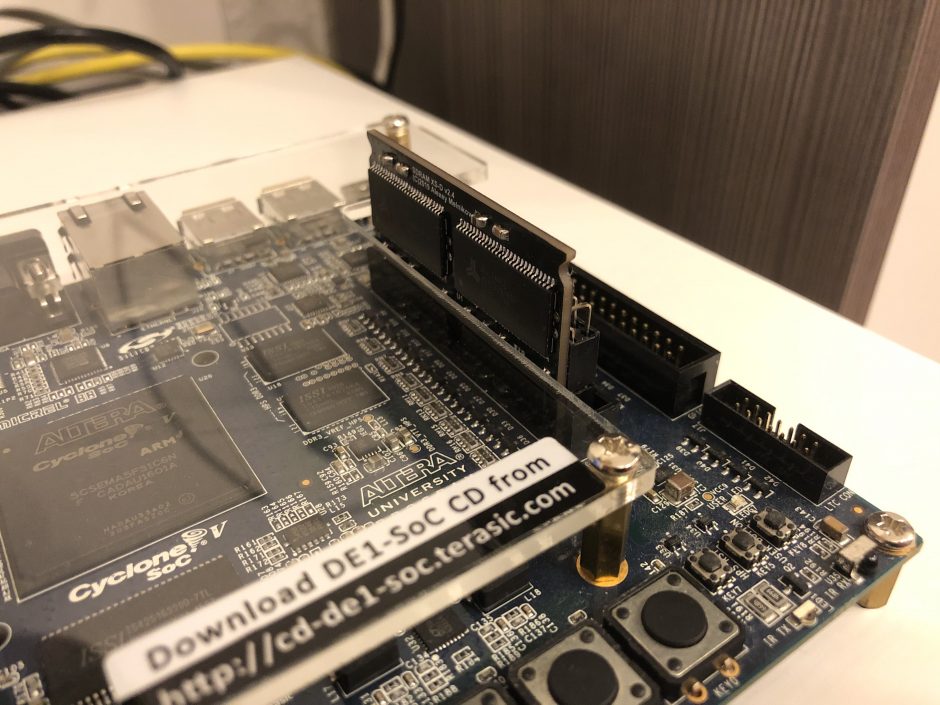

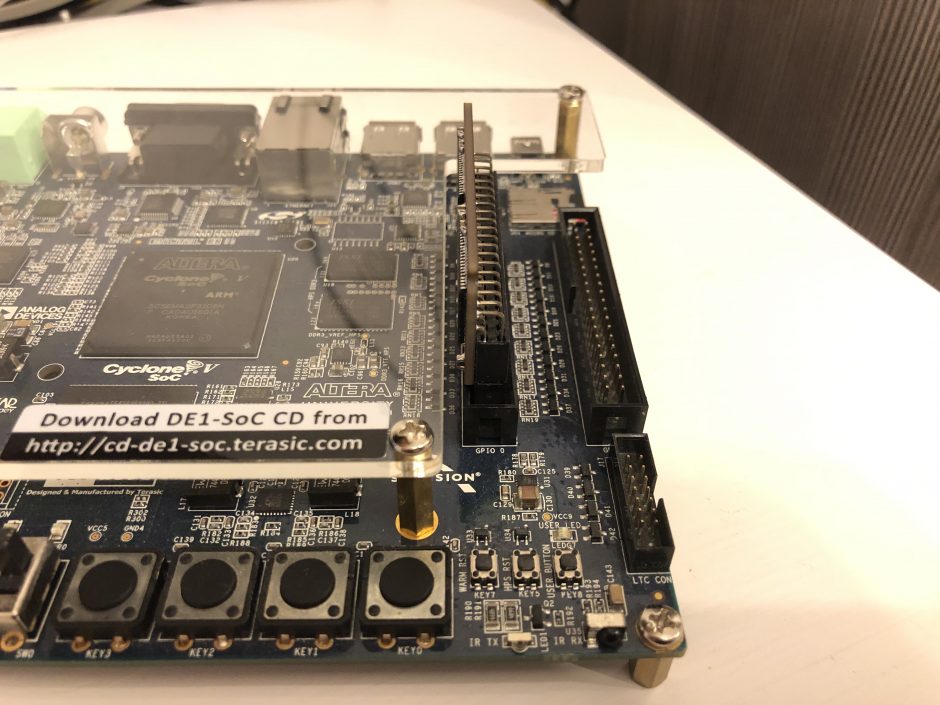

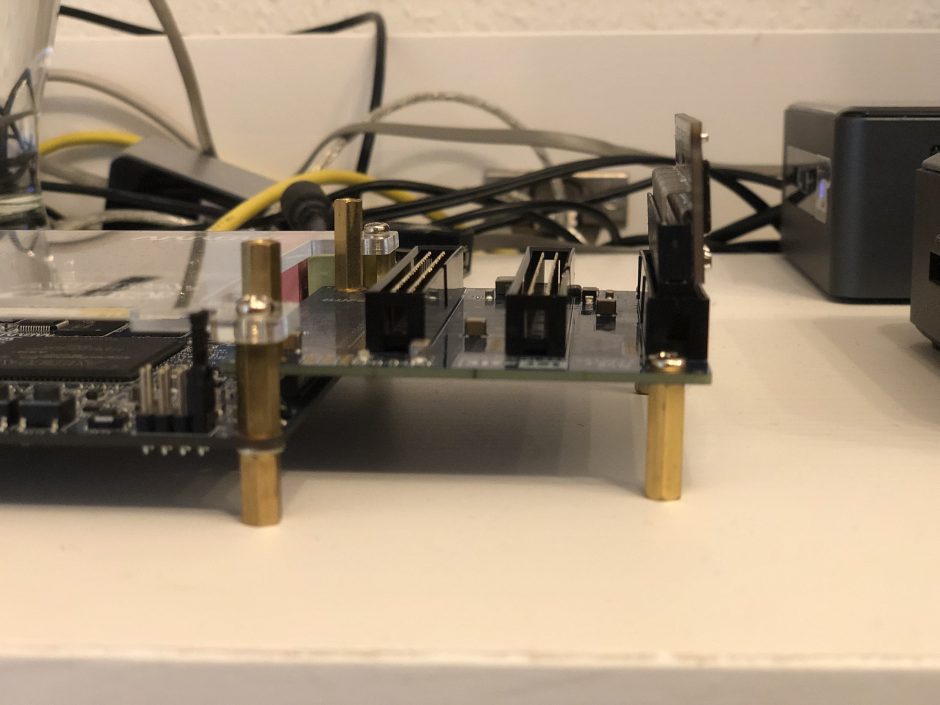

MiSTer SDRAm board without riser:

Left:

Back:

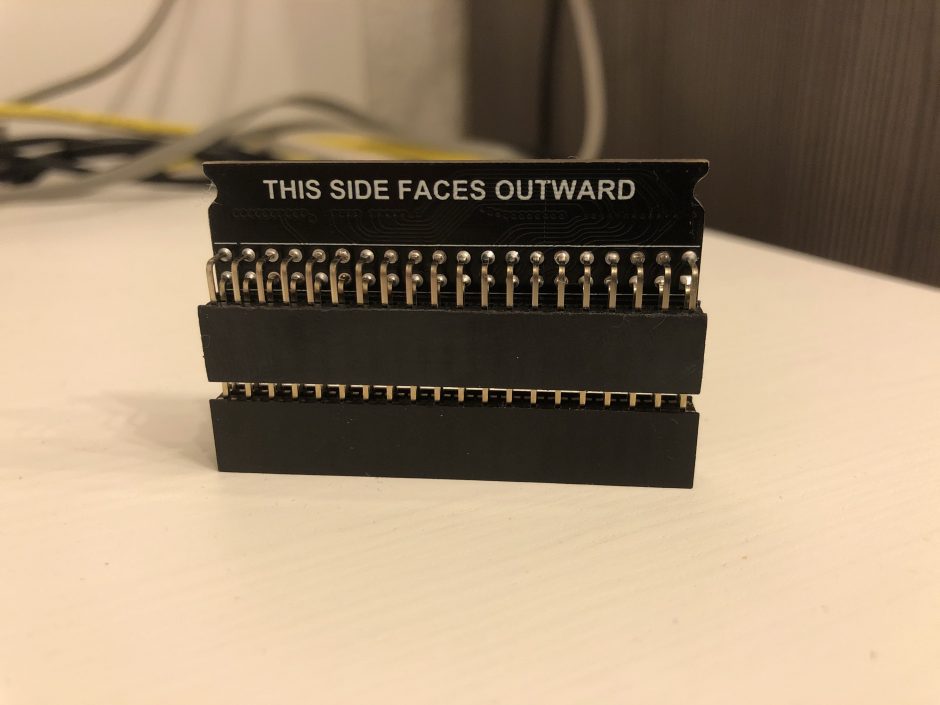

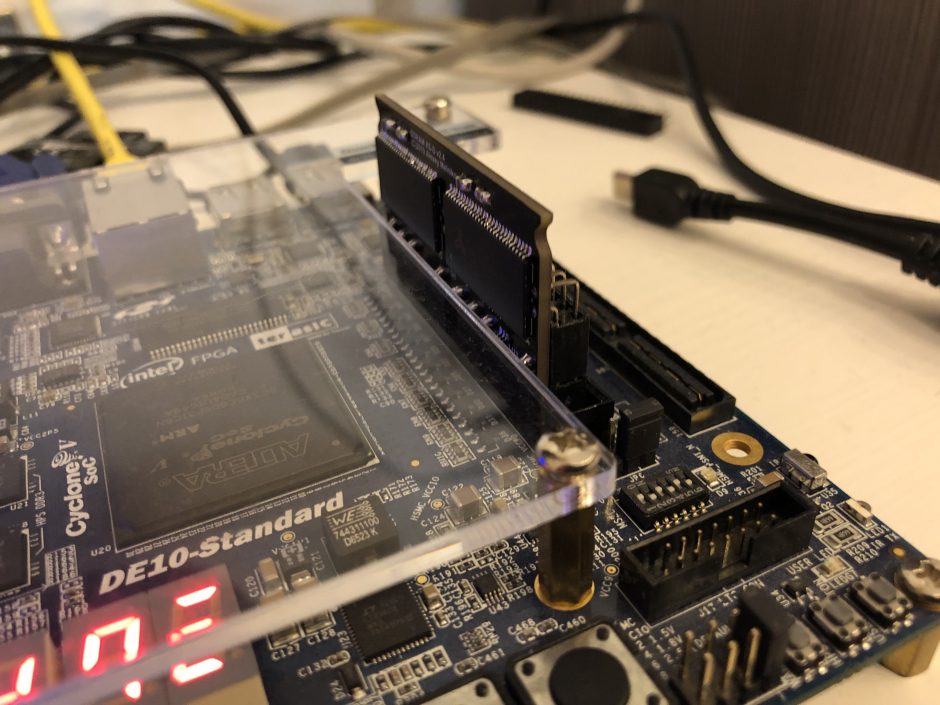

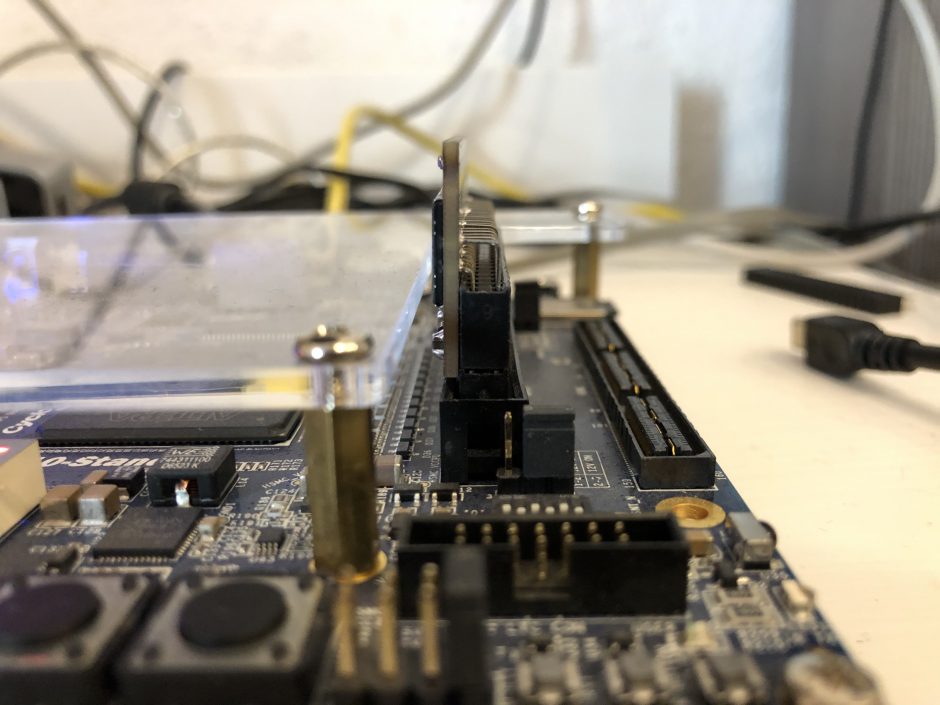

You will have to install a GPIO 40 pin riser first to your MiSTer SDRAM :

Once the Riser is placed, ready to use the expansion module:

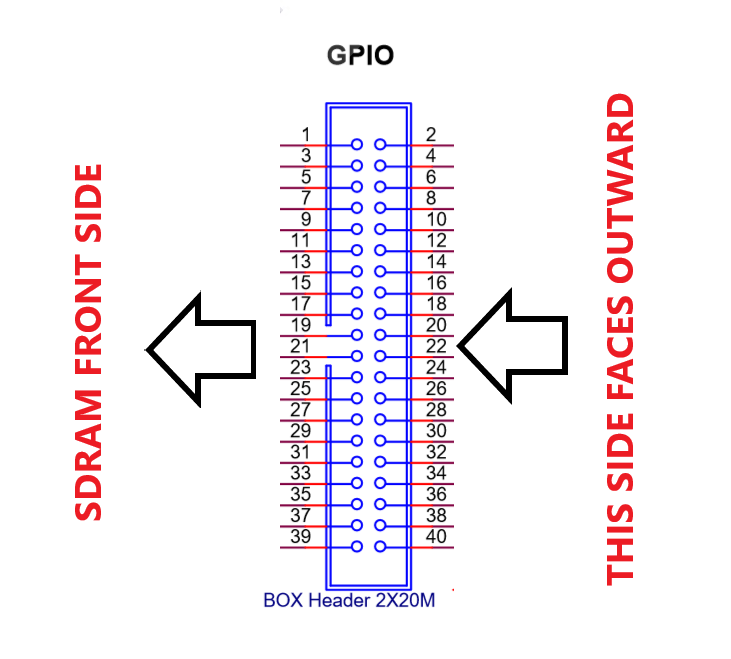

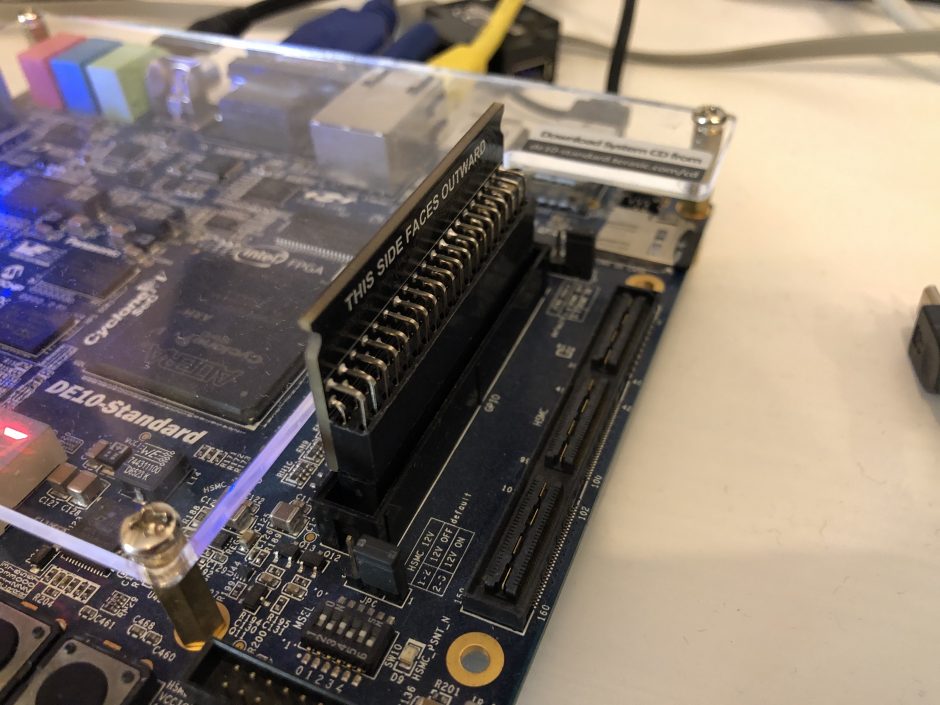

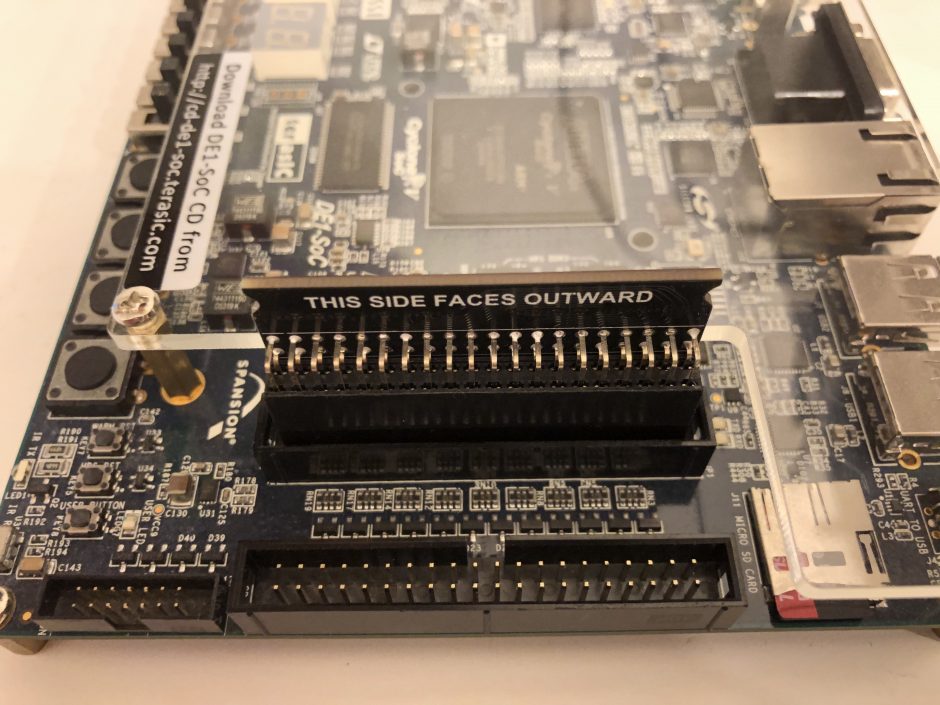

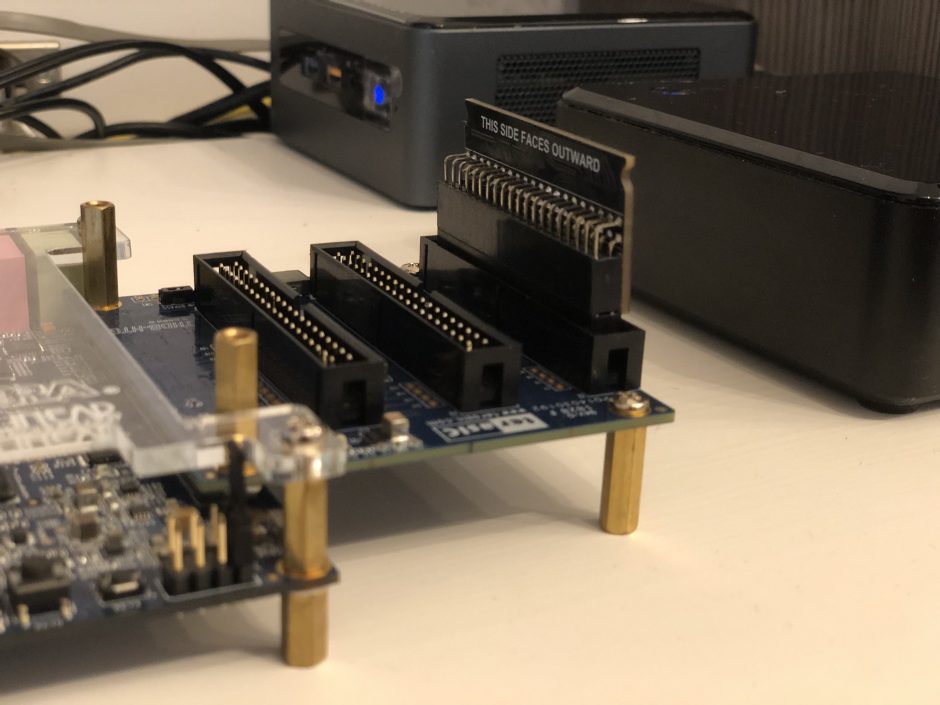

SDRAM placement direction – please read this section with caution!

You have to make sure when you inserting the SDRAM Board to your standard GPIO header FPGA, the directions have to be matching.

SDRAM Front Side – where you see the RAM chip, has to be on the holey side of the GPIO port.

Note: if you mistakenly connect to the opposite side, it can damage your SDRAM board/FPGA – due to the reason that GPIO port 11/12 and 30/29 ports are non replacable ports (Ground and Voltage ports)

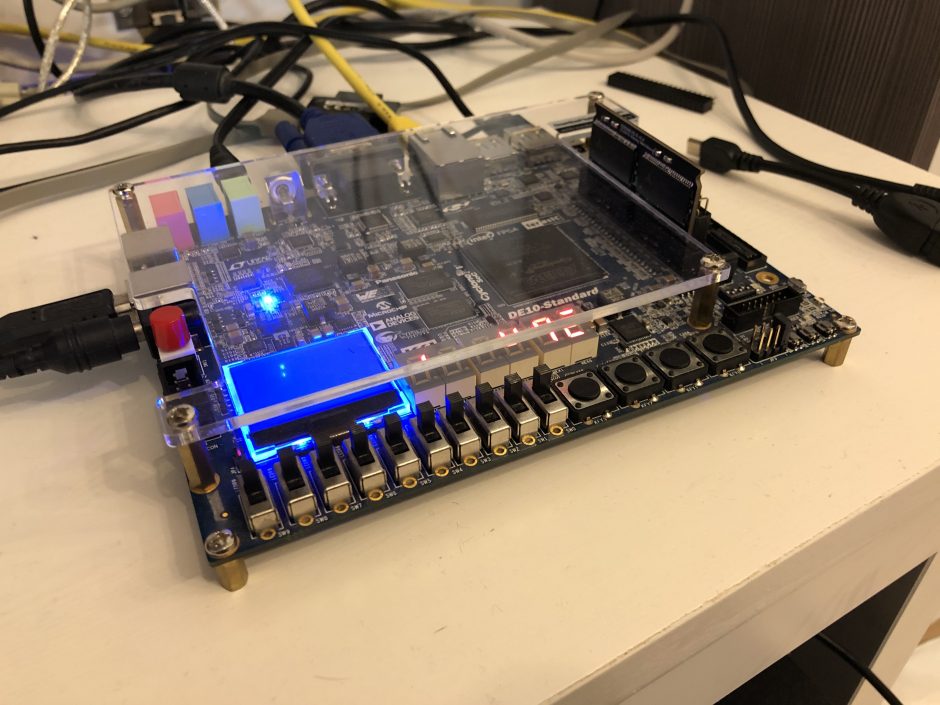

MiSTer 128MB SDRAM placement to DE10-Standard FPGA board through GPIO riser

Place the SDRAM board to GPIO0 / JP1:

MiSTer 128MB SDRAM placement to DE1-SoC FPGA board through GPIO riser

Place the SDRAM board to GPIO0 / JP1:

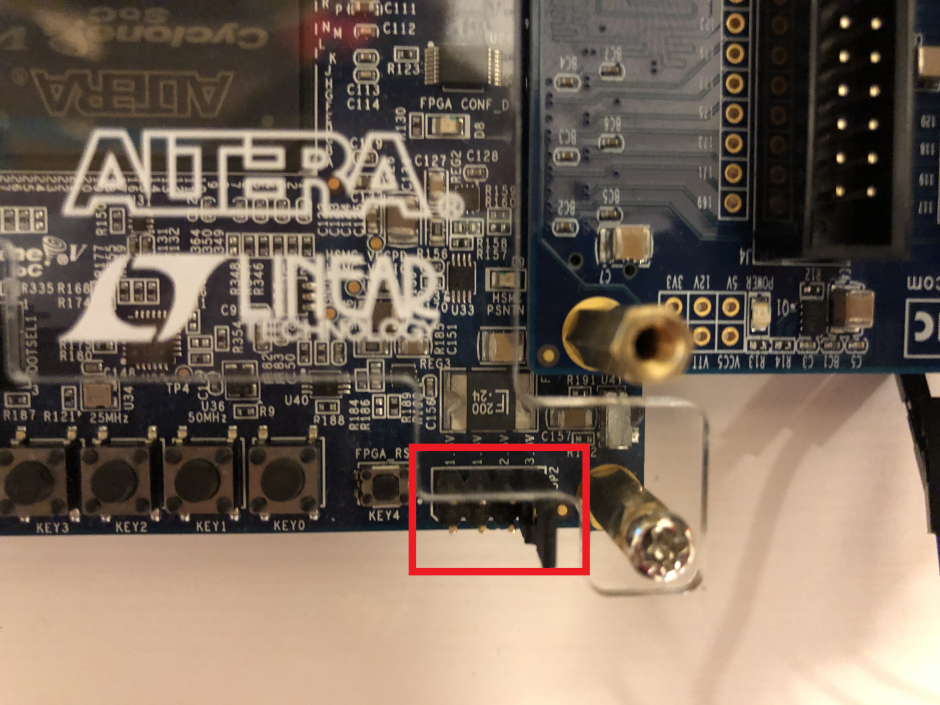

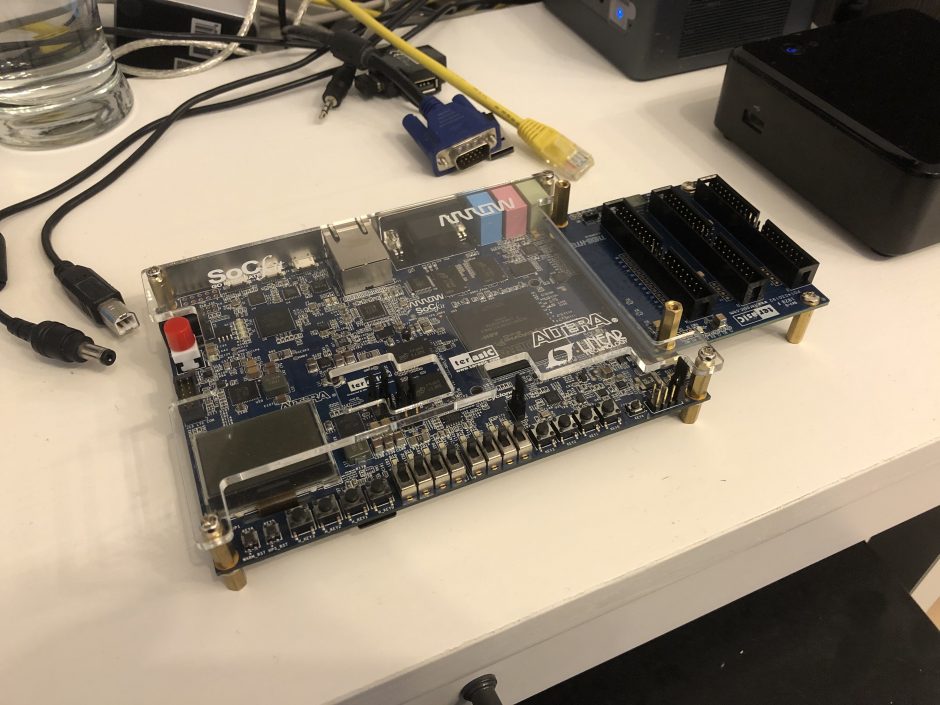

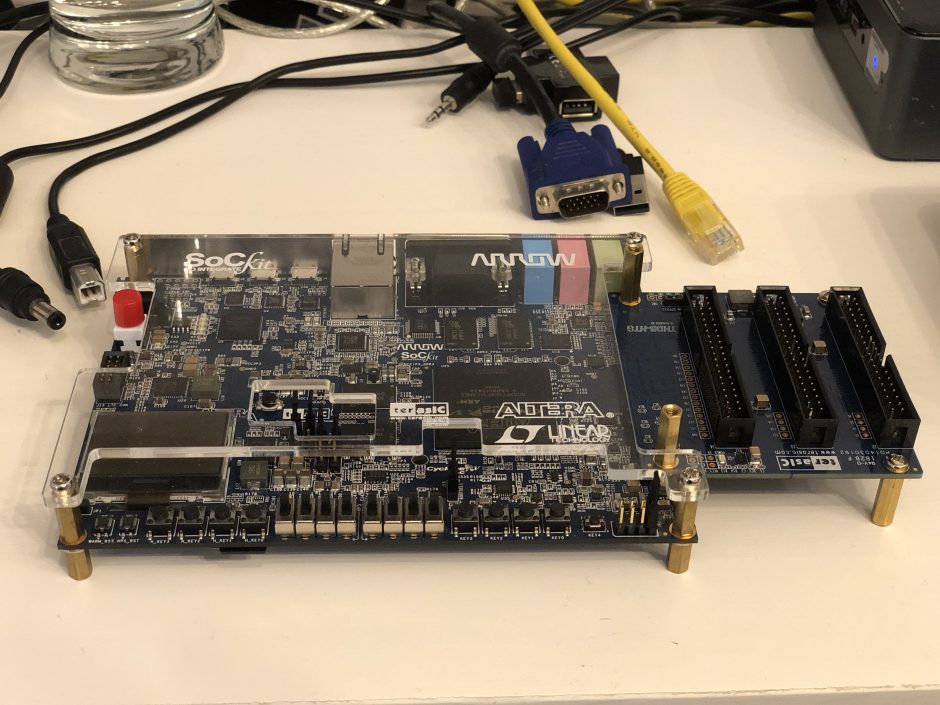

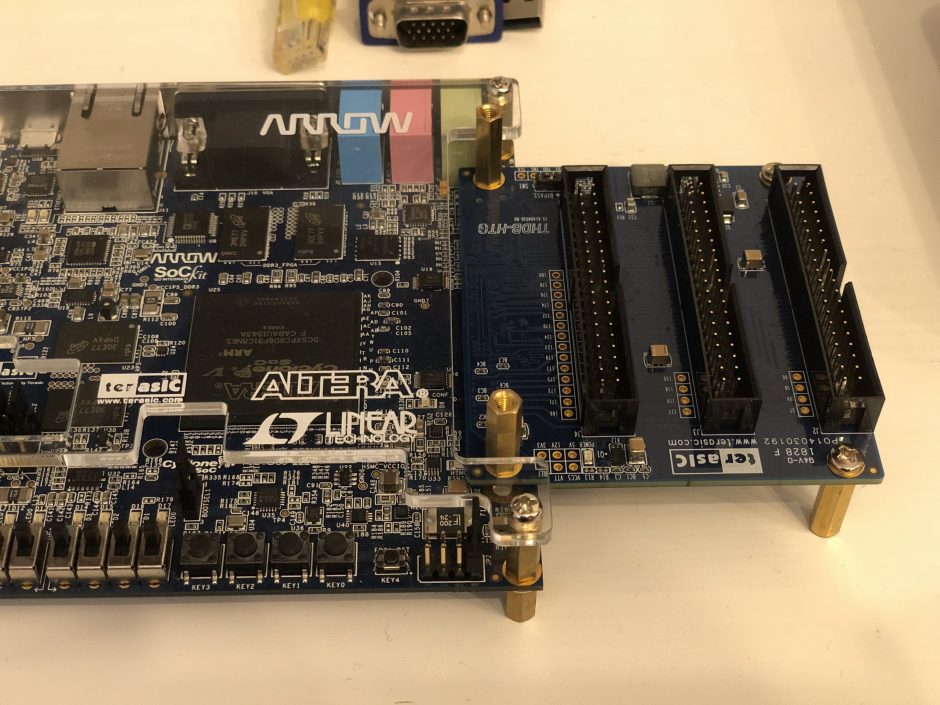

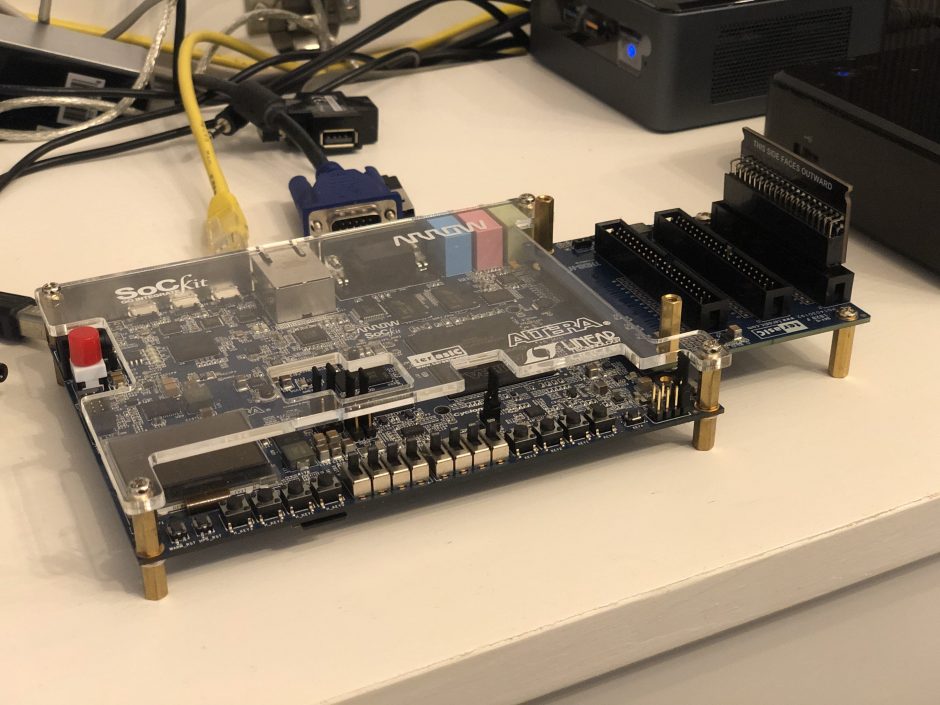

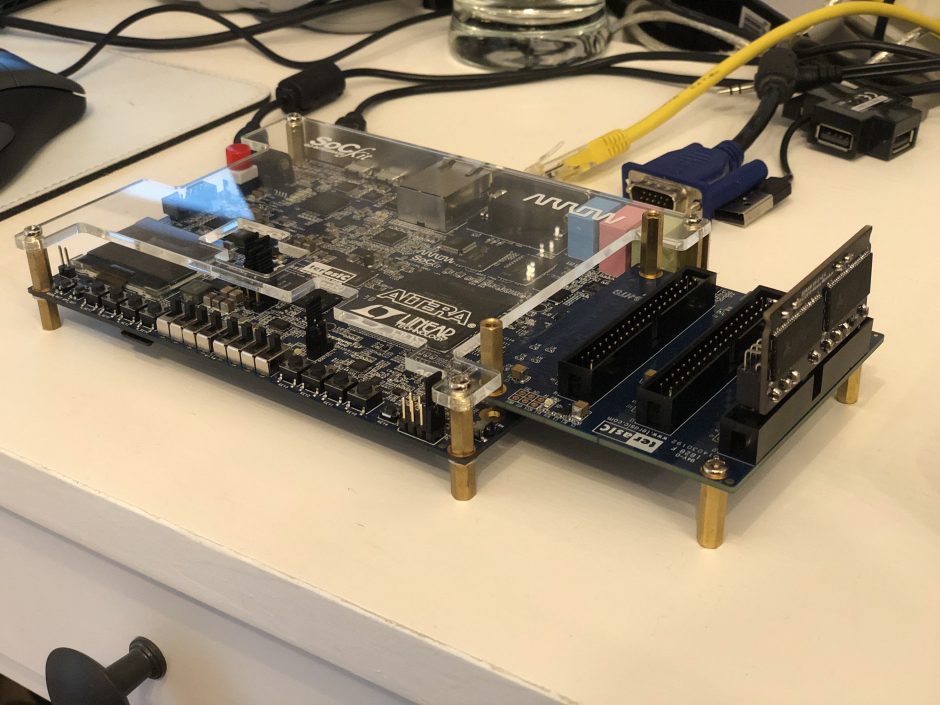

MiSTer 128MB SDRAM placement to Arrow SoCKit FPGA board with the support of GPIO HSMC/HSTC daughter board and GPIO port riser

First of all you have to switch Arrow SoCKit FPGA’s HSMC iostandard switch – JP2 – to 3.3V mode.

The SDRAM Board operates at 3.3V, while the HSMC expansions boards default iostandard setting is just 2.5V, that is why you have to force with this switch to operate at 3.3V.

If you miss the mentioned iostandard 3.3V setup on JP2 jumper, it will damage the attached peripherials and SDRAM Board memory!

Attach the HSMC daughter board to the Arrow SoCKit FPGA

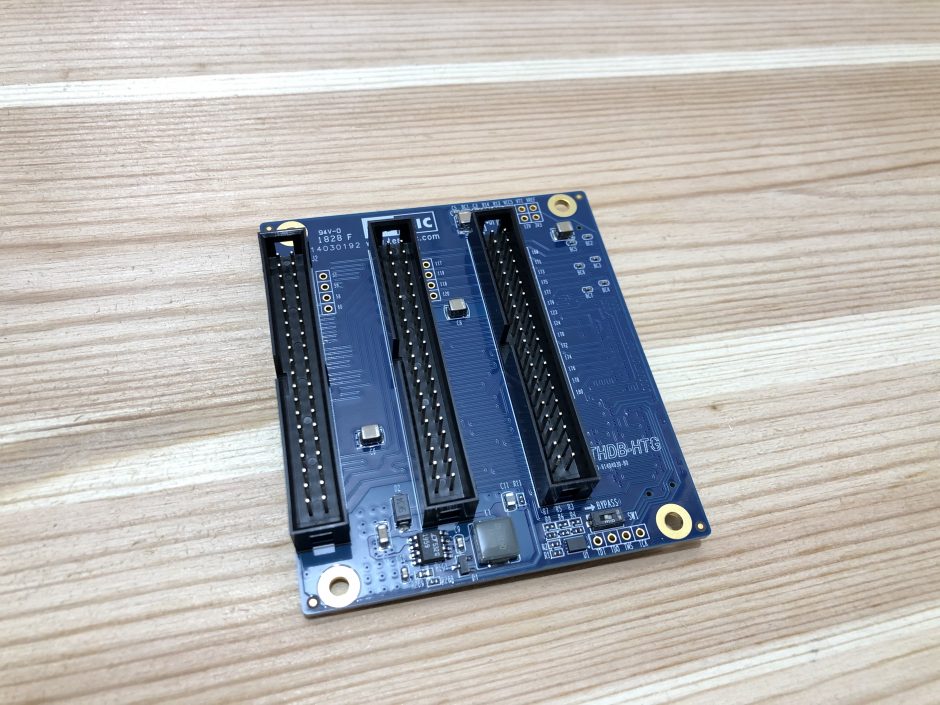

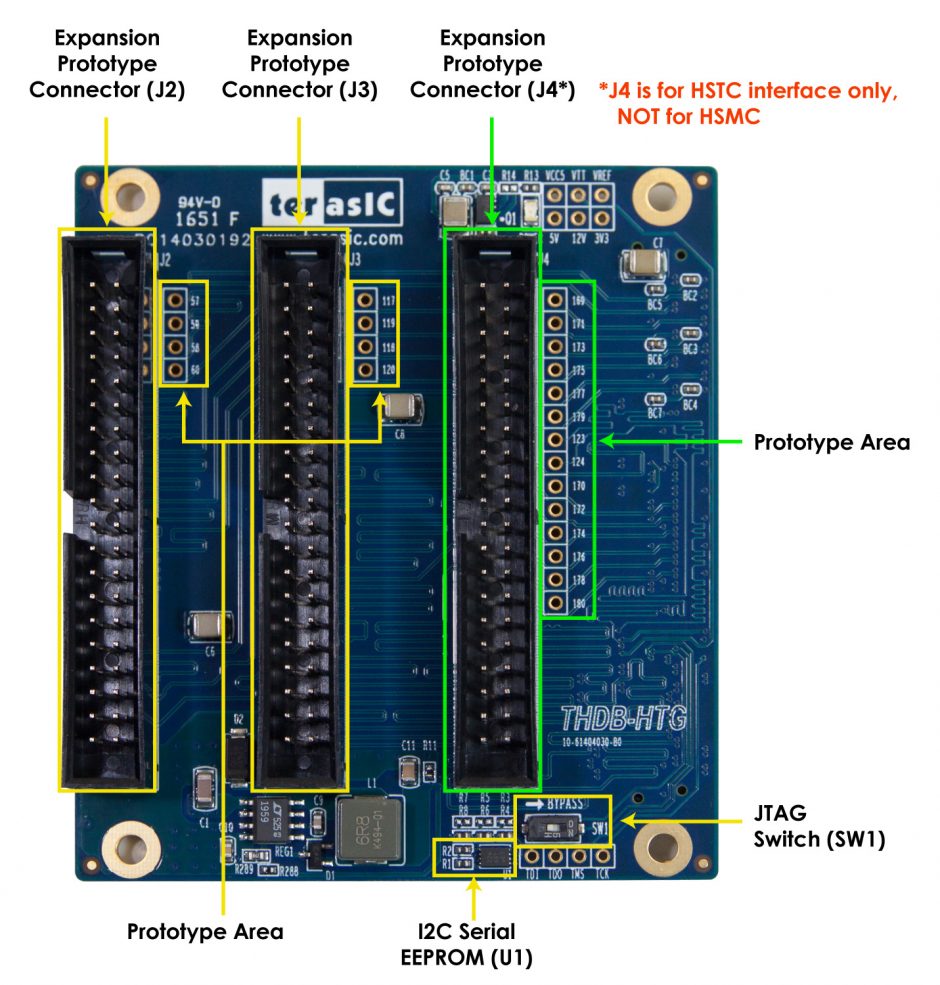

You need to have a HSMC male connector equipped HSMC-GPIO adaptor board

Connect the HSMC connecter to your Arrow SoCKit:

Place the SDRAM board to GPIO slot “JP2”- be careful, the HSMC daughter board is upside-down compared to the FPGA direction, so the GPIO ports are upside down as well, you need to be careful of placing the SDRAM to the right GPIO direction, holey side is on the opposit side:

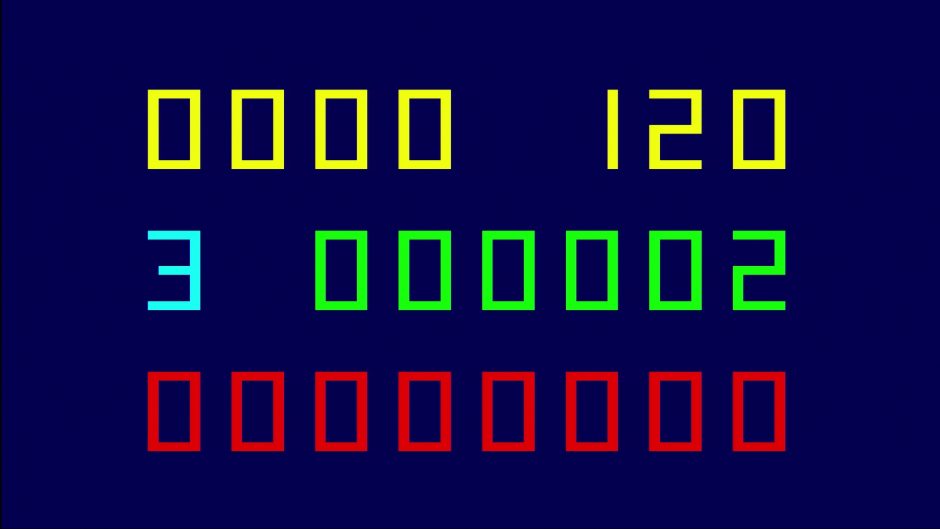

You can run some memory tests, with the GPIO ports you should reach roughly 120MHZ SDRAM speed – the GPIO wire placement on DE10-Standard/De1 SoC bords have longer pin route than DE10-Nano, so do not expect faster MHZ rates:

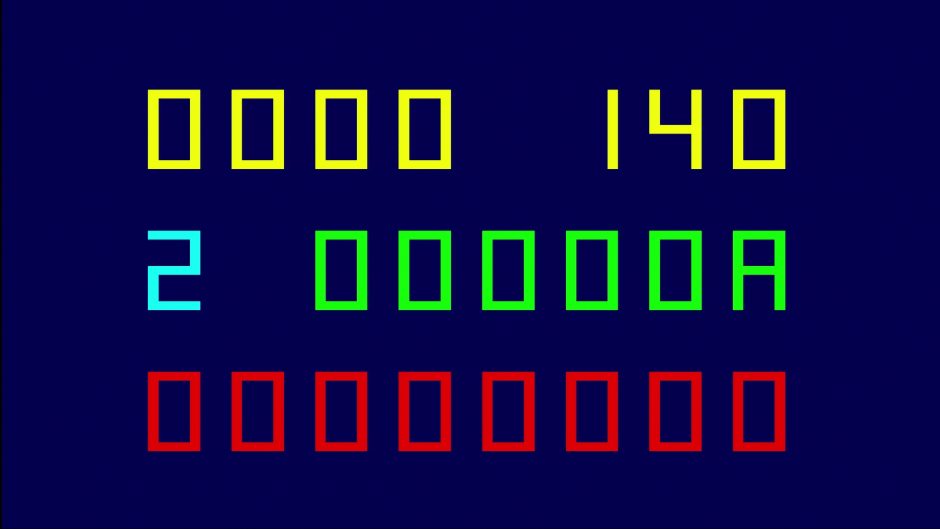

If you benchmark the internal DE10-Standard/D1-SoC memory, you should be able to reach 140MHZ

Download Links:

DE10-Standard:

Updated Main MiSTer:

https://github.com/MiSTer-DE10-Standard/Main_MiSTer

MiSTer Menu Core for External SDRAM Board Support on JP1 GPIO pin port:

https://github.com/MiSTer-DE10-Standard/Menu_MiSTer

MemTest release for 128MB Ram on JP1 GPIO pin:

https://github.com/MiSTer-DE10-Standard/MemTest_MiSTer

NeoGeo core release which supports 128MB SDRAM Board on JP1 GPIO pin:

https://github.com/MiSTer-DE10-Standard/NeoGeo_MiSTer

DE1-SoC:

Updated Main MiSTer:

https://github.com/MiSTer-DE1-SoC/Main_MiSTer

MiSTer Menu Core for External SDRAM Board Support on JP1 GPIO pin port:

https://github.com/MiSTer-DE1-SoC/Menu_MiSTer

MemTest release for 128MB Ram on JP1 GPIO pin:

https://github.com/MiSTer-DE1-SoC/MemTest_MiSTer

NeoGeo core release which supports 128MB SDRAM Board on JP1 GPIO pin:

https://github.com/MiSTer-DE1-SoC/NeoGeo_MiSTer

Arrow SoCKit:

Updated Main MiSTer:

https://github.com/MiSTer-Arrow-SoCKit/Main_MiSTer

MiSTer Menu Core for External SDRAM Board Support on J2 HSMC card port:

https://github.com/MiSTer-Arrow-SoCKit/Menu_MiSTer

MemTest release for 128MB Ram on J2 HSMC card port:

https://github.com/MiSTer-Arrow-SoCKit/MemTest_MiSTer

NeoGeo core release which supports 128MB SDRAM Board on J2 HSMC card port:

https://github.com/MiSTer-Arrow-SoCKit/NeoGeo_MiSTer