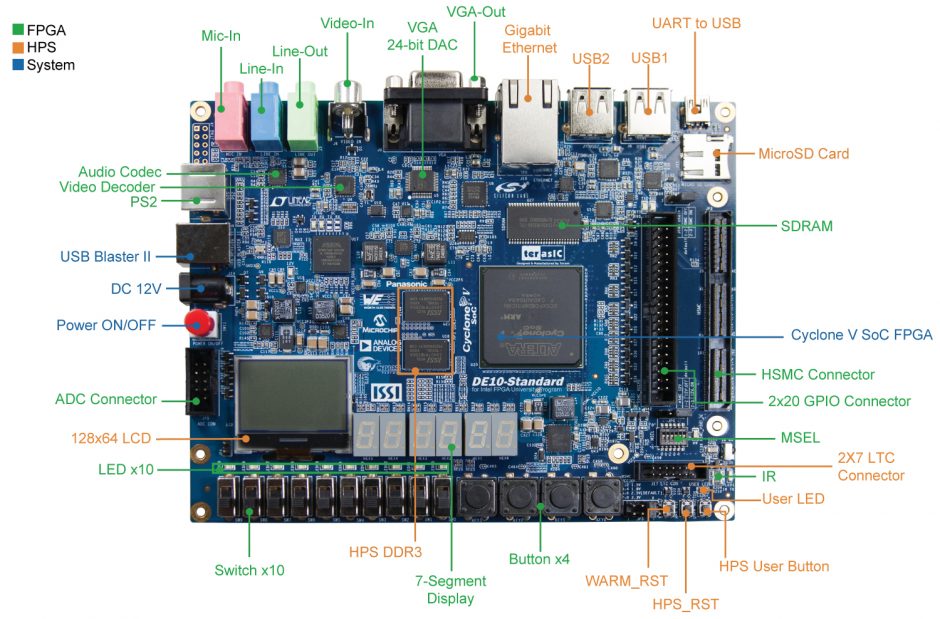

MiSTer is a cool project published originally by Sorgelig on Github and the FPGA code + project binaries only focused on DE10-Nano board, which is a great board: low price + HDMI output and ability to expand with SDRAM and Daughter board for VGA and Audio jack, but my idea was simply to support other FPGA boards as well, to port the code that supports the big brothers as well, such as DE10-Standard and later DE1-Soc. These boards feature point of view rich for an FPGA platform: 64MB SDRAM, VGA and audio output.

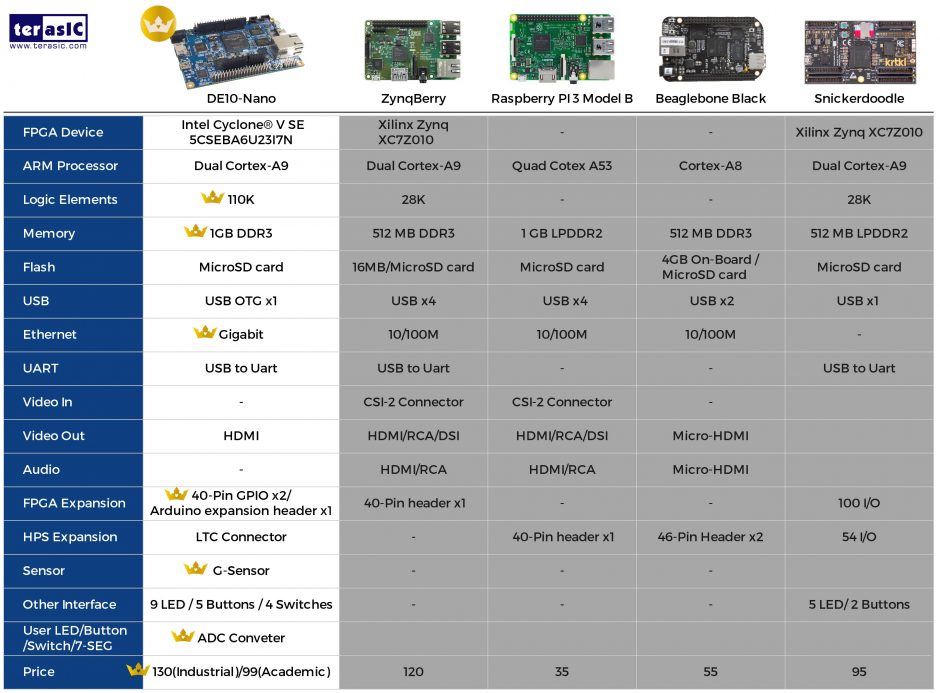

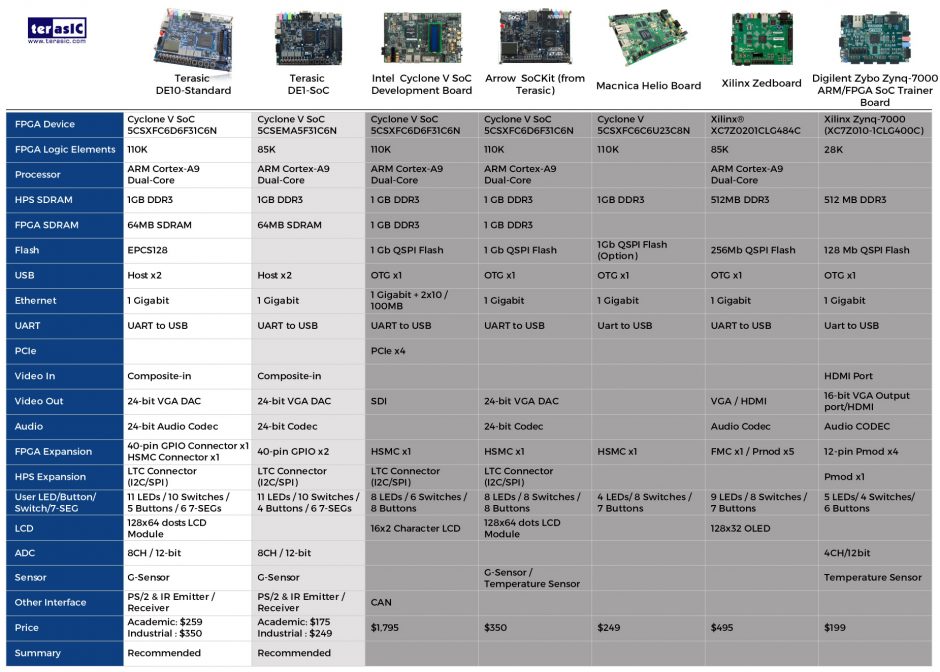

Quick re-cap about features of FPGA boards Nano vs Standard vs SoC

You can see from the feature list that DE10-Standard has the following additions comparing to DE10-Nano:

- built-in 64 MB SDRAM (this is important for retro cores emulation)

- built-in 24bit VGA output DAC for crystal clear VGA retro output

- built-in Wolfson 8731 audio DAC for crystal clear analogue output

- UART-USB onboard bridge from a FT232R chip – for easy serial console on USB port

- 2X standard size USB port that you can use to plug your USB Keyboard / Controller directly without necessary need of USB Hub

- Cyclone V SX SoC—5CSXFC6D6F31C6N: it has 110K LEs, 41509 ALMs – biggest on the consumer market this segment – similar like DE10-Nano.

The only thing the board is not equipped with is HDMI. If you build multi function FPGA board for running retro computers – who cares?

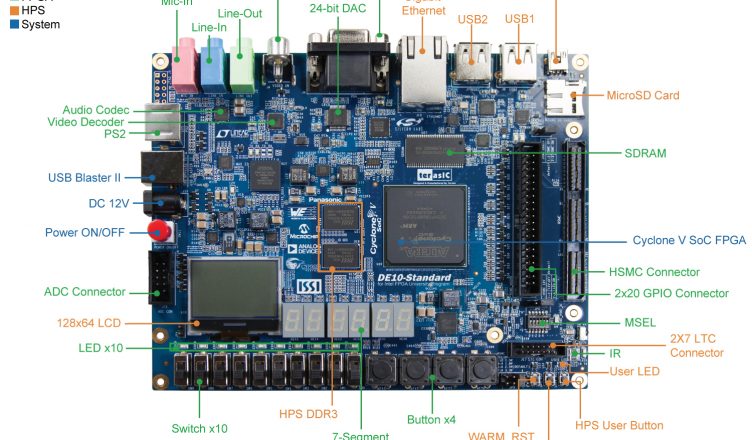

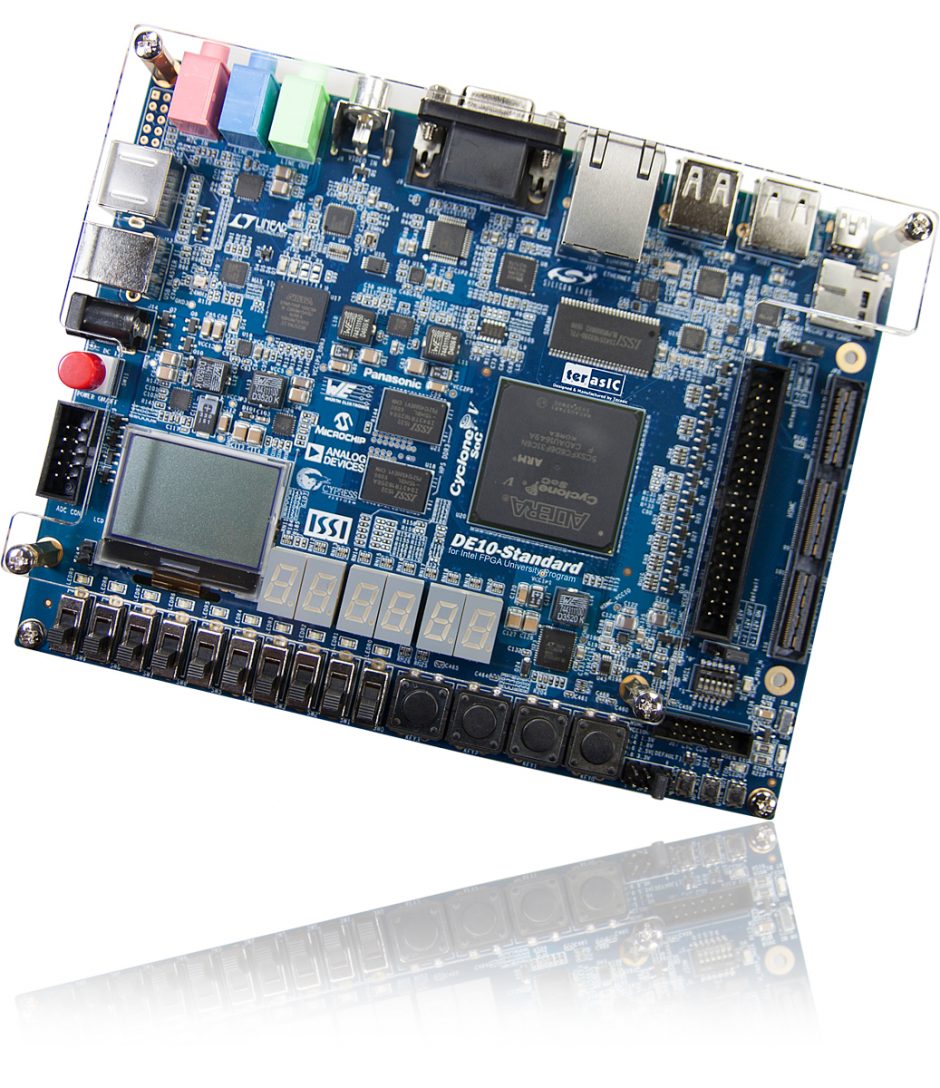

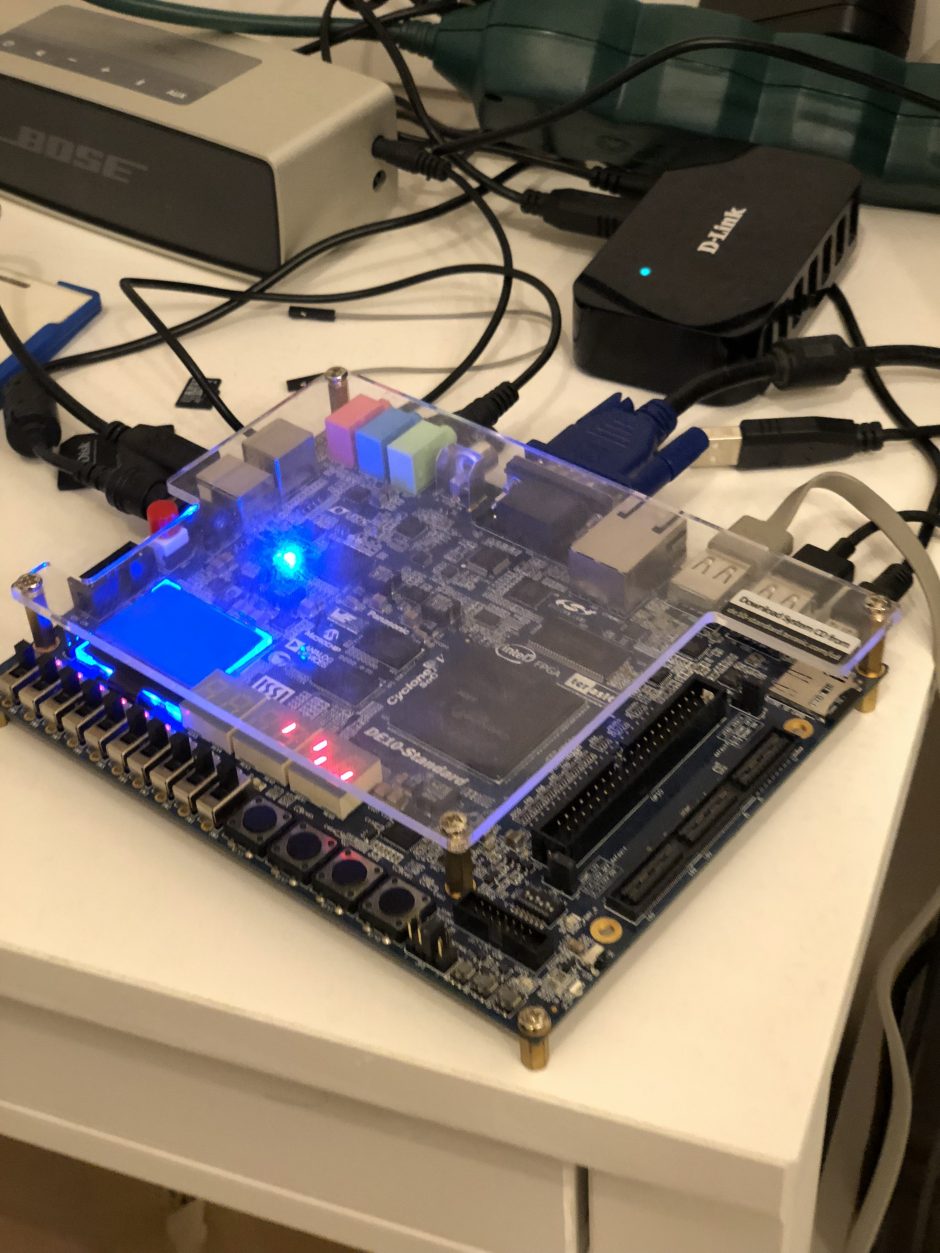

DE10-Standard is a beautiful and feature rich board to start with:

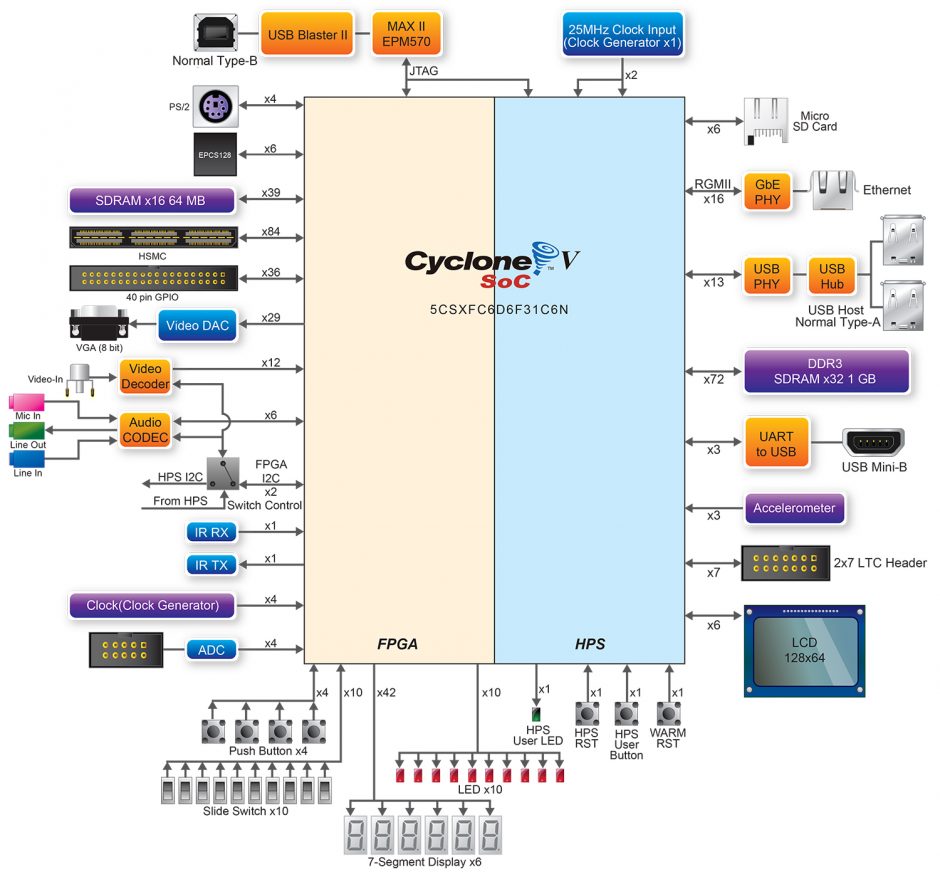

DE10-Standard architecture is similar like Nano, dual architecture: FPGA which running the binary and HPS (ARM which running the Linux)

Used Quartus software to port / develop further the original MiSTer code.

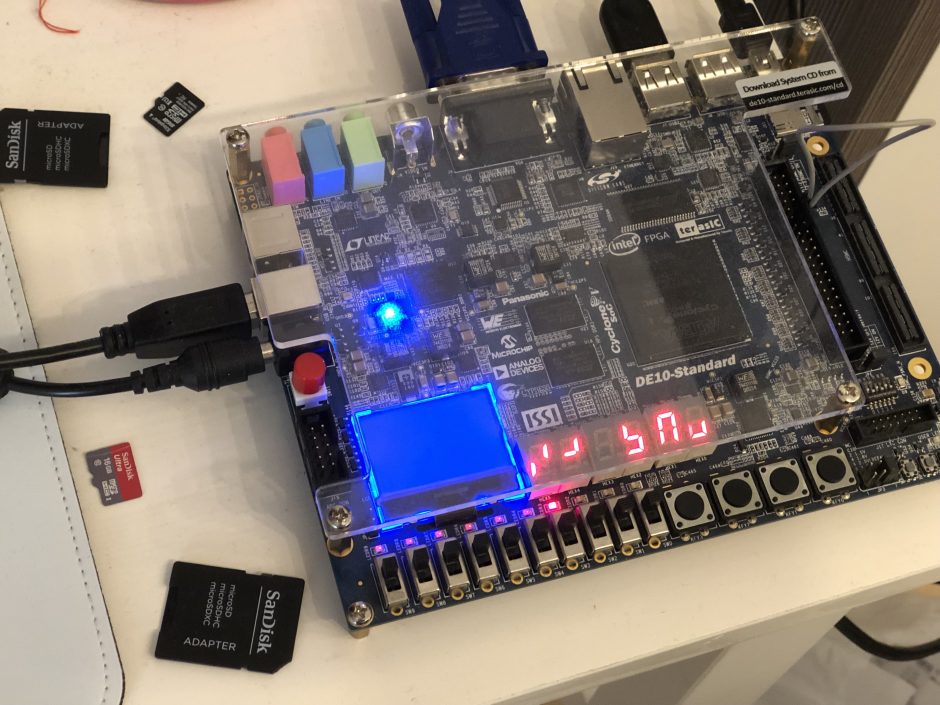

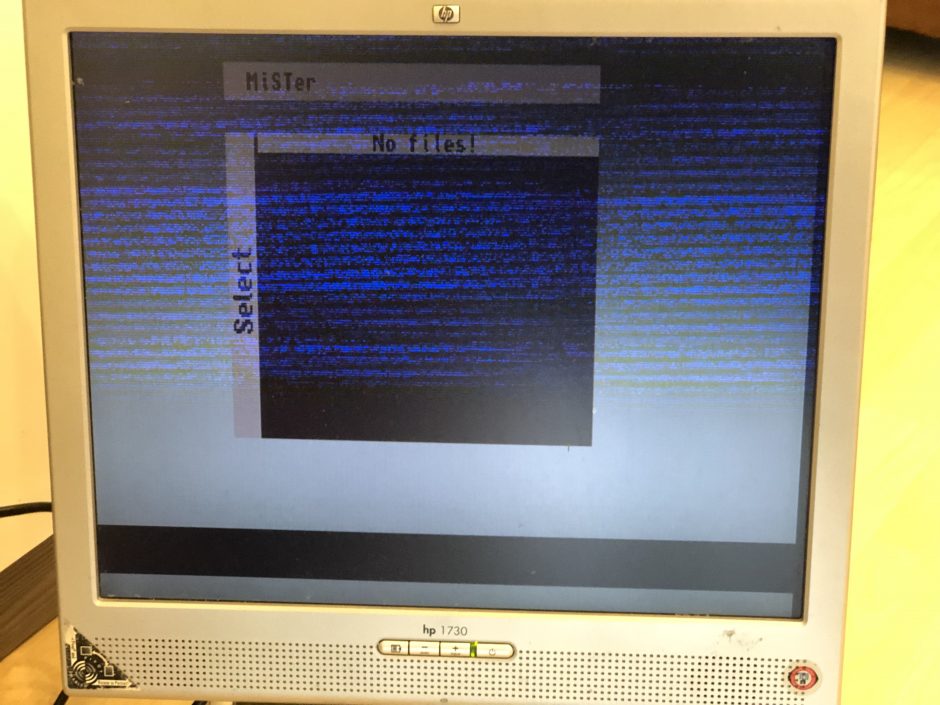

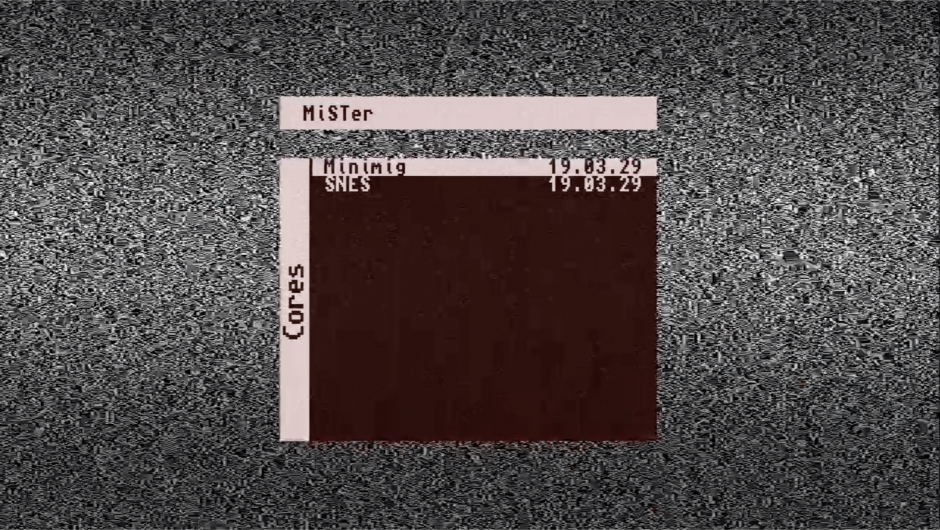

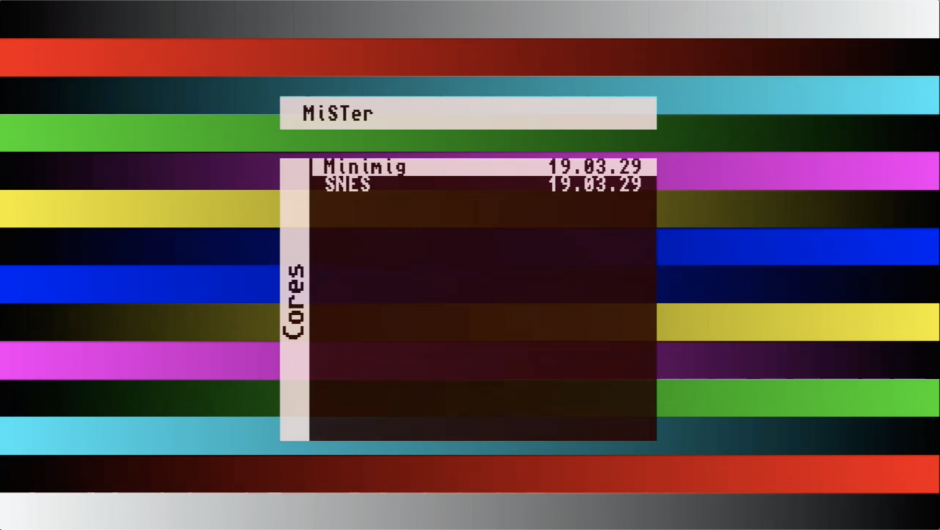

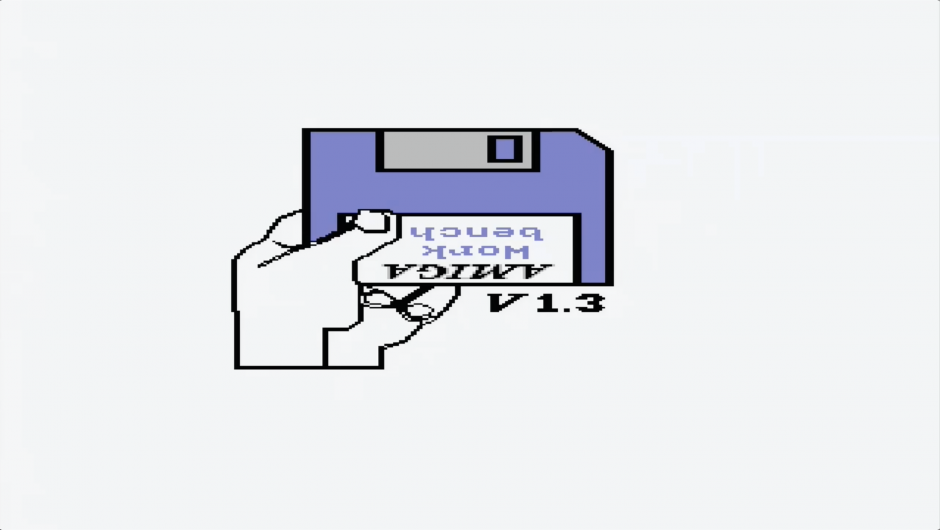

Steps of the development progress in pictures:

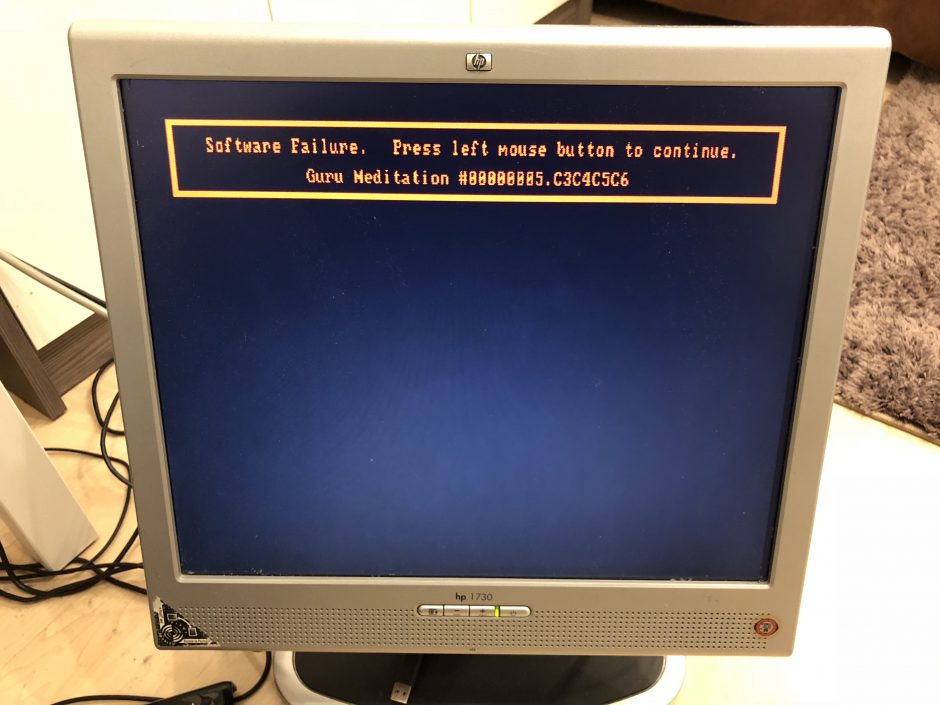

Console log of booting up with a basic Minimig-Core:

* Original Minimig by Dennis van Weeren

* Updates by Jakub Bednarski, Tobias Gubener, Sascha Boing, A.M. * Robinson & others

*

* FileLoad(open) File:/media/fat/config/MINIMIG.CFG, error: -1.

* Can not open configuration file!

*

* Setting config defaults

*

* >>> No config found. Using defaults. <<<

* CPU: 68000, Chipset: OCS-A500, ChipRAM: 1mb, FastRAM: 2mb, * * SlowRAM: none

* Open up to 10 input devices.

*

* Checking HDD 0

* HDD 0: not present

*

*

* Checking HDD 1

* HDD 1: not present

*

* CPU clock : normal

* Chip RAM size : 1mb

* Slow RAM size : none

* Fast RAM size : 2mb

* Floppy drives : 2

* Floppy speed : fast

*

*

* A600/A1200 IDE HDC is disabled.

* Master HDD is not present.

* Slave HDD is not present.

*

* Exiting bootloader…

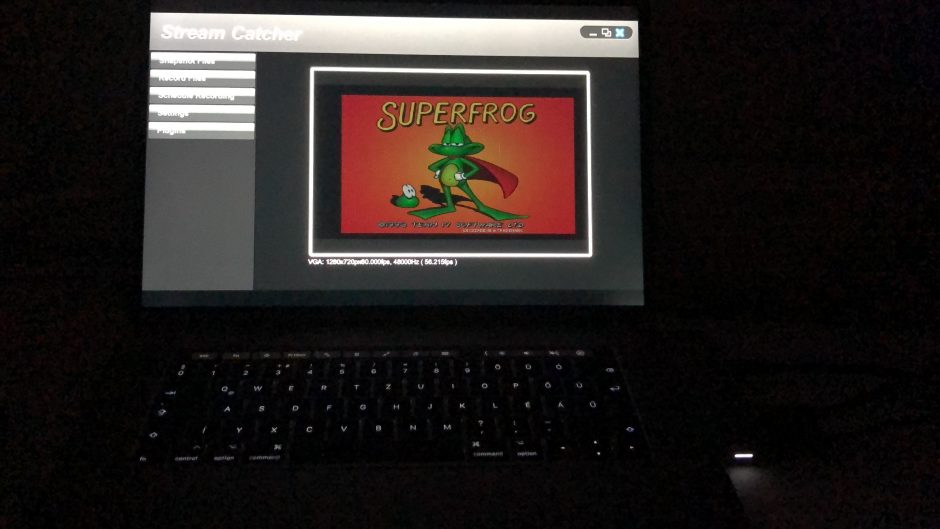

The board is capable now to run MiSTer Core – Minimig-Aga

The picture brightness still low.

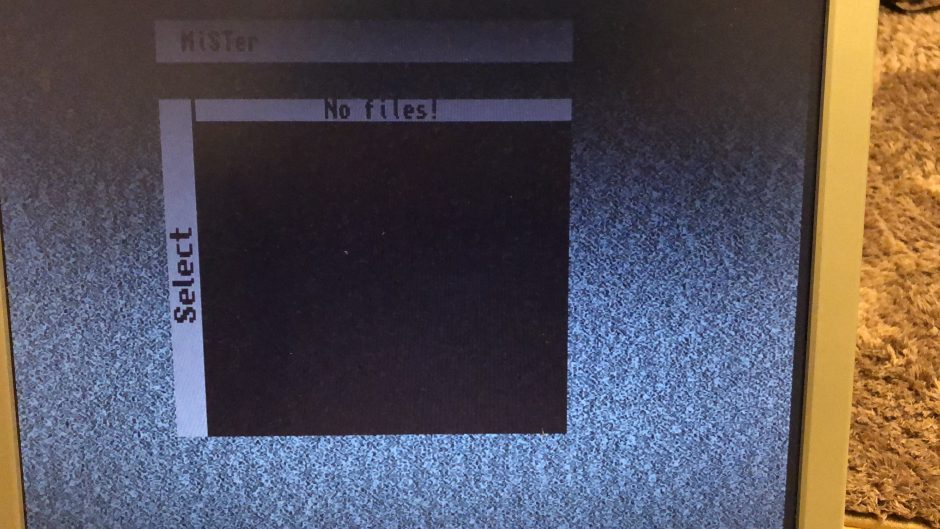

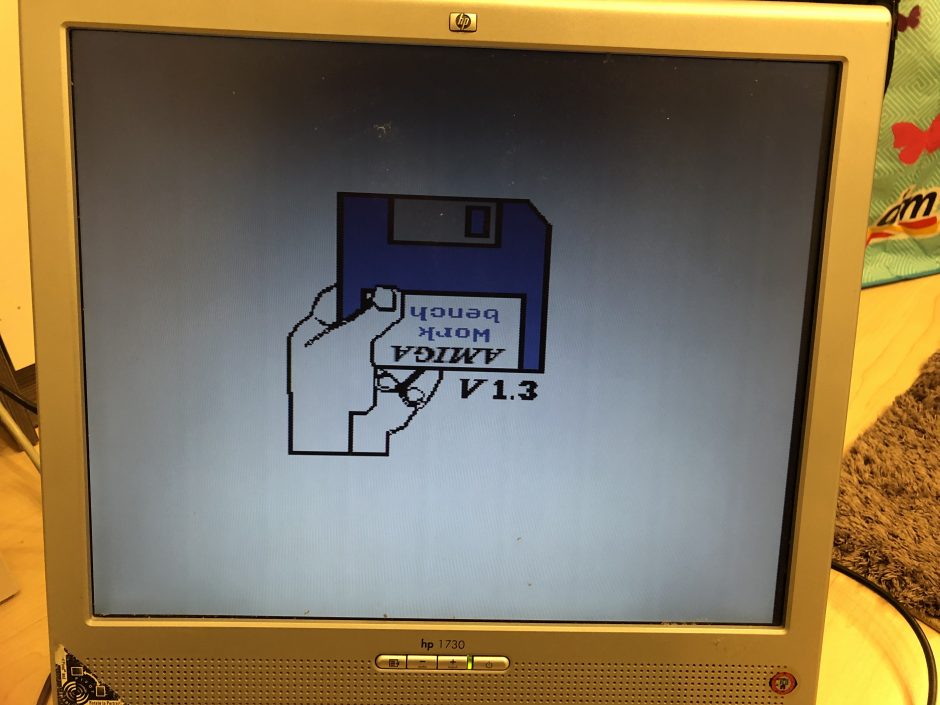

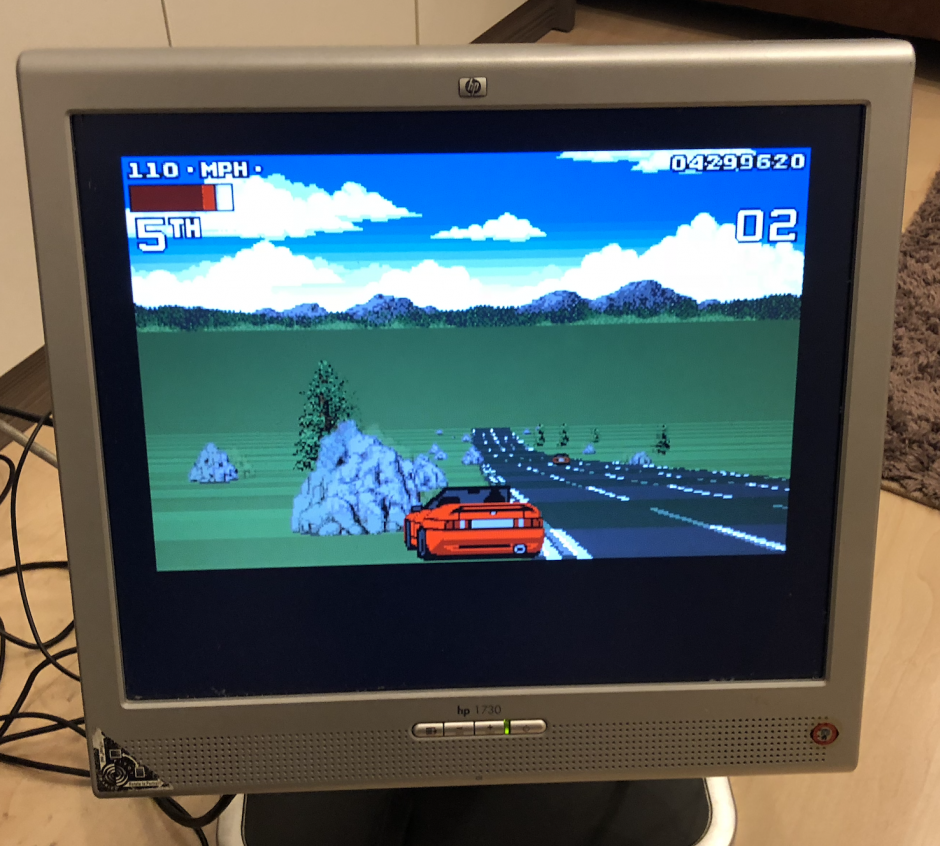

The DE10-Standard FPGA board is running now without the jumper wire:

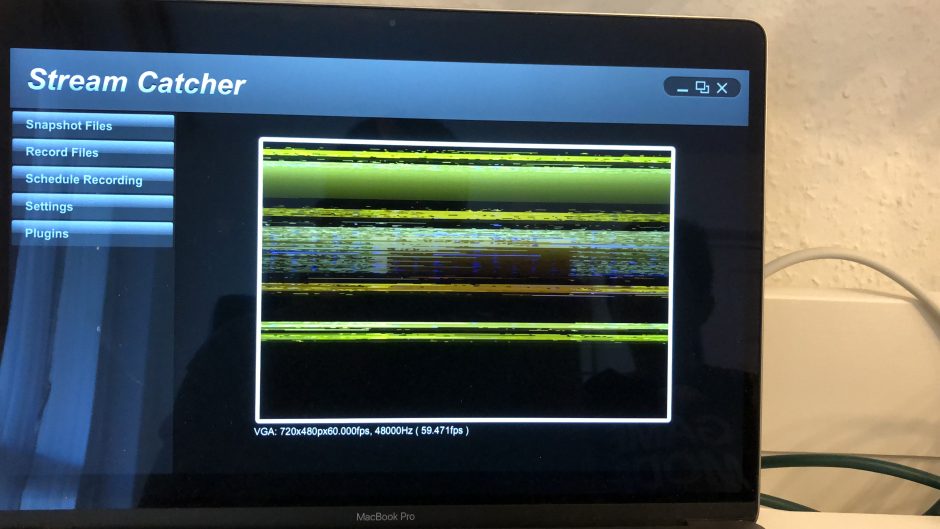

VGA DAC picture is now Crystal Clear:

DE10-Standard port of MiSTer released on Github

https://github.com/MiSTer-DE10-Standard/Main_MiSTer/wiki